A Study on Lightening Asynchronous Pipeline Controller for Reusable Delay Path Synthesis

Main Article Content

Abstract

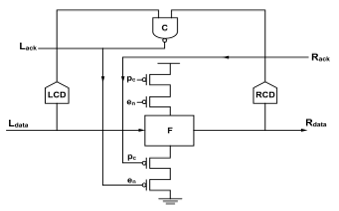

To improve on plan endeavors, for example, the advancement of synchronizing protocols, asynchronous layouts have been widely used to computerize the plan of asynchronous circuits for low-power and high-performance applications. Pipeline layouts, specifically, are generally utilized in current, high-performance systems. This examination shows how normal rationale circuits and MSI circuits might be planned utilizing proficient asynchronous pipelines. Different standard rationales and MSI circuits are utilized in the performance examination of the different formats. Since the QDI formats can distinguish both positive and negative advances, they are exceptionally lenient of interaction changes. With regards to assembling resiliences and configuration changes, QDI circuits are shockingly lenient. The objective of this study is to sum up a period suspicion made by staticizers for QDI rationale. The focal point of this work is on limiting circuit space and power utilization without forfeiting dependability.