Designing Architecture of Embedded System Design using HDL Method

Main Article Content

Abstract

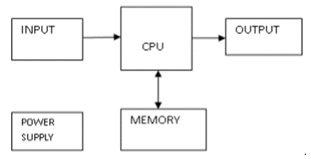

the vendors and researchers are under pressure to enhance the embedded system design methodology due to the time-to-market pressure and productivity gap. Register Transfer Level (RTL), the conventional design method, is inadequate for the needs of embedded system design. A different approach is required to deal with the RTL problem. In this paper, we propose a new approach to hardware embedded system modeling that makes use of Transaction Level modeling to boost the efficiency of the design process (TLM). When it comes to design abstraction levels, TLM is the next step up after RTL. Time to design and design precision are two of the metrics tracked. Avalon and Wishbone buses, both System on Chip buses, were utilized in the actualization of the RTL model.TLM and RTL model improvement performance metrics. The results of the experiments show that Avalon RTL's performance is improved by a factor of 1.03 for 3-tiers, 1.47 for 4-tiers, and 1.69 for 5-tiers when the new design methodology is used.Wishbone RTL increases performance by a factor of 1.12 on a 3-tier system, 1.17 on a 4-tier system, and 1.34 on a 5-tier system. The pattern of these outcomes demonstrates a rising standard of design practice.