# A Study on Lightening Asynchronous Pipeline Controller for Reusable Delay Path Synthesis

# Kajol Khatri

MS- Computer Science, University of Texas at Arlington, Texas kxk7899@mavs.uta.edu

# Dr. Anand Sharma

Asst. Prof., Department of CSE, Mody University of Science and Technology, Lakshmangarh https://orcid.org/0000-0002-9995-6226 anand\_glee@yahoo.co.in

## Keywords

Protocols, asynchronous, pipelines, high-performance, systems, etc.

# Abstract

To improve on plan endeavors, for example, the advancement of synchronizing protocols, asynchronous layouts have been widely used to computerize the plan of asynchronous circuits for low-power and high-performance applications. Pipeline layouts, specifically, are generally utilized in current, high-performance systems. This examination shows how normal rationale circuits and MSI circuits might be planned utilizing proficient asynchronous pipelines. Different standard rationales and MSI circuits are utilized in the performance examination of the different formats. Since the QDI formats can distinguish both positive and negative advances, they are exceptionally lenient of interaction changes. With regards to assembling resiliences and configuration changes, QDI circuits are shockingly lenient. The objective of this study is to sum up a period suspicion made by staticizers for QDI rationale. The focal point of this work is on limiting circuit space and power utilization without forfeiting dependability.

Received by the editor: 01.08.2022 Received in revised form: 18.10.2022 Accepted: 04.11.2022

### 1. INTRODUCTION

Pipelining is a fundamental methodology that might be used in simultaneous PC systems. In this technique, huge capability blocks are separated into a progression of more modest blocks, registers are acquainted all together with truly separate each block, and the framework clock is applied to all registers. Conversely, asynchronous systems don't involve a worldwide clock in any of their tasks. Thus, a convention should be created for the communication of neighboring stages, notwithstanding selections of information encoding and stockpiling parts. Also, the plan of an unequivocal conveyed control structure should be finished. This assortment, when taken all in all, capabilities as a model or skeleton to facilitate the singular parts of an asynchronous pipelined framework. From that point forward, asynchronous pipelines have had broad application, going from the early business illustrations and flight reproduction systems of Evans and Sutherland, whose LDS-1 (Line Drawing Framework 1) was first sent to Bolt, Beranek and Newman (BBN) in 1969, to the central methodologies of Throw Seitz. The essential idea and plan of an asynchronous pipeline were introduced by David Muller in his original paper from 1963. From that point forward, asynchronous pipelines have been generally involved Each asynchronous between stage association capabilities as a correspondence channel, frequently conveying information and control data all the while [1].

Information (and in some cases a solicitation control signal) is passed from left on to right, and a recognize control signal is sent from right to left. Correspondence is frequently bidirectional and is achieved utilizing a handshaking convention. The fundamental qualifications among simultaneous and asynchronous pipelines are brought out by the correlation displayed in this realistic. The clock propels the entire framework in secure move toward coordinated pipelines, and that implies that each datum thing passes to the following stage on the dynamic clock edge. Thus, the pipeline carries out the role of a coordinated shift register that contains figure blocks. Furthermore, the complete deferral of the framework's basic ways should be lower than the framework's set clock time frame; if not, the framework won't work as expected. As an immediate outcome of this, all stages will regularly about have postpones that are adjusted. Asynchronous pipelines, then again, don't have a focal clock. The movement of information things is facilitated on a phase by-stage premise locally at every area [2]. The guideline of stream is performed consequently through asynchronous pipelines. Indeed, even in settings with fluctuating velocities, the sub-current and flood gambles are naturally moderated by the presence of a handshaking convention. Then again, coordinated pipelines have no stream control worked in of course. Generally speaking, express credit-based strategies that need extra registers or confounded decoupled hook control are utilized to permit simultaneous stream control. At each step, the slow down signal, which is used for back pressure, is likewise expected to be matched up to the clock. Taking everything into account, asynchronous pipelines possibly utilize dynamic measures of power when it is really required. In other words, exchanging action doesn't occur beyond the handling of information things; in any case, stages and their control are in a condition of tranquility. This methodology takes into account the upside of robotized clock gating to be accomplished, yet without the requirement for extra instrumentation. This might be finished at any degrees of granularity in the plan, especially while managing continually moving traffic designs.

Moreover, the utilization of asynchronous pipelines normally disposes of the prerequisite for the dispersion of a worldwide clock.

# 2. LITERATURE REVIEW

The extraordinary performance of the asynchronous pipeline structures examined in this article has been demonstrated by both as of late delivered business chips and exploratory chips. With explicitly, a test gadget intended for a fine-grained pipelined most prominent normal divisor (GCD) estimation had the option to show Mousetrap pipelines that were equipped for working at 2.1 GHz in 130-nm innovation. [3] Heave pipelines have shown exceptionally high performance because of its lowabove convention. [4] This remembers ongoing discoveries of 4 GHz for 90-nm innovation for the Boundlessness test chip at Sun Labs. [5] Wheeze pipelines have been utilized in various applications (presently Prophet Labs). PCHB pipeline type is utilized to execute the information way in the business Nexus crossbar switch created by Support Microsystems. This switch works at 1.35 GHz and is made utilizing 130-nm innovation. [6] Finally, the HC style is utilized to construct the speed-basic information stream in а trial mixed synchronous/asynchronous FIR channel gadget that was worked at IBM Exploration. This chip works at 1.8 GHz in 180-nm innovation. [7-8] Exploration has been directed on various different help instruments, plan cycles, augmentations, and applications for high-performance asynchronous pipelines. Among them are devices for framework level performance examination [9] and improvement [10-11], notwithstanding some model computerized computer aided design union schedules. Late pipelined applications incorporate high-performance FPGAs, Ethernet switch chips, iterative divisions, FIR channels, and NoCs. Lowabove testing techniques have likewise been introduced [12-14]. Coordinated strategies have additionally been introduced, and these techniques draw from the asynchronous plan approach. [15-16] These philosophies utilize asynchronous thoughts of back pressure and the administration of extended worldwide pathways inside planned systems. Furthermore, a desynchronization approach can make asynchronous circuits from coordinated netlists by trading the clock for handshaking channels. This interaction is known as the blend of asynchronous circuits.Asynchronous pipelines loan themselves especially well to the execution of dynamic rationale for various reasons. Specifically, the entryway type that is utilized in powerful asynchronous systems is commonly a completely staticized domino. In this design, every unique door yield comprises of an essential inverter that is connected to it as well as a powerless criticism inverter, which together make up a lightweight stockpiling component. The impacts of spillage, charge sharing, and commotion are actually hindered by such entryways' high degree of invulnerability. Moreover, DI-encoded asynchronous information pathways can exquisitely acknowledge defer variances achieved hv vulnerability in control sharing and clamor [17-18]. This is conceivable because of the way that singular pieces can show up with any slant without gambling with defilement. As a result of this, unique rationale has seen far reaching application in various as of late delivered high-performance asynchronous business items. A few instances of these items incorporate Ethernet switch chips fabricated by Support Microsystems (right now 65 nm) and FPGAs made by Achronix Semiconductor (90-nm down to 22-nm innovations).

#### 3. RESEARCH METHODOLOGY

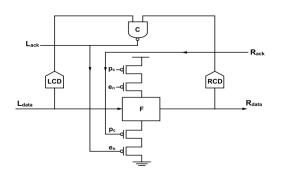

PreCharged Half Cradle: The Schematic Is Displayed in Figure.1 Underneath (PCHB). Frail adapted half-support input-end indicator is utilized to check legitimacy and lack of bias (WCHB). This sort of locator has a LCD at its feedback and a RCD at its result.

Figure 1: PreCharge Half Buffer

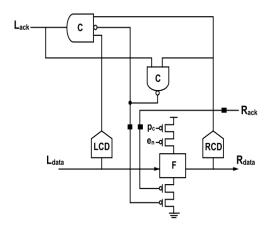

The capabilities block doesn't need to be feebly adapted assuming it is to assess ahead of all sources of info being gotten. In any case, the layout doesn't give an affirmation signal Need until after all data sources have been gotten and the surveyed outcome has been disposed of. In this way, a C-component is being utilized by the LCD and RCD to make the affirmation signal. The affirmation Signal is a functioning low sign since the C-component is transforming its rationale. Second, two additional inverters are in many cases used to cradle the inner sign en that controls the capability block before the Need signal is conveyed. The precharge half cradle (PCHB) is ideal for supported rationale, but the compose catch-and-convey half cushion (WCHB) is helpful for supports. For two data sources and one result, as found in Figure 1, the PCHB layout has a two-progress dormancy and a fourteen-change process duration. Recognizing it from the WCHB is the way that it can tell when data sources are unbiased on Lack↓ as opposed to Rack↓. Thusly, a greater number of sources of info is conceivable since nonpartisanship identification all through many changes doesn't influence inertness. An example of a completely energized cradle with precharging is displayed in Figure 2. Despite the fact that it requires an additional state variable, the PCFB is more simultaneous than the PCHB on the grounds that its L and R handshakes reset all the while.

Figure 2: Pre-Charged Full Buffer

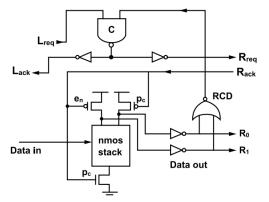

To diminish the size of the change stack in the capability block, another pipeline layout is proposed. This layout gets rid of the PCHB's inside en signal. As should be visible in Figure 3, this new QDI pipeline configuration is known as a Decreased Stack PreCharged Half Cradle (RSPCHB). The RCD block is improved by tapping its contributions before the result inverter, and a NAND entryway is used instead of an OR door. Decreasing superfluous simultaneousness is one manner by which the RSPCHB format supports eliminating the inside empower signal. LCD and RCD yields are joined in the PCHB layouts through a C-component to deliver the affirmation signal Need. Consequently, the requirement for capability blocks to be feebly

**ActaEnergetica**

molded is killed, and handshake convention can be coordinated with the legitimacy and impartiality of both info and result information. In any case, this substitution presents more simultaneousness than is totally needed, as it requires the utilization of the en signal. At the point when one of the information channels supplies information, the non-feeble adapted capability block might give a result. Subsequently, the join's RCD attests the outcome. Then again, every future stage might take in information, evaluate it, and state the two its LCD and RCD results and affirmation signal. This join might be recognized, yet it will not precharge until en is affirmed. To keep the circuit from being rashly charged after the info stages have been recognized, the signal is declared. en

Figure 3: R Reduced Stack PreCharged Half Buffer

The RCD will not deactivate during the precharge in view of the postponement. Also, the C-component won't ever give the affirmation. Assuming affirmation signals have been created and recognized at any step after the join, the en sign might be safely removed. Considering that the join is currently the show's bottleneck, any postpone in the affirmation would meaningfully affect performance. The shortfall of a LCD and the more modest stack size of the capability block in RSPCHB is an advantage since it diminishes capacitive burden thus brings about significantly faster generally performance. This performance support comes to the detriment of a solitary extra wire of correspondence between stages.

#### 4. RESULT AND DISCUSSION

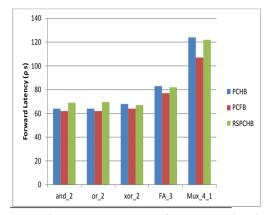

Figure 4 displays the PCFB, PCHB, and RSPCHB template circuits' delay.

Figure 4: Forward latency of standard circuits across PCFB, PCHB, and RSPCHB templates

The PCHB has 6.5% less postponement than the remainder of the example circuits. Since Re and Le are converged in an unmistakable celement in the PCHB as opposed to in the information rail stacks, dormancy is decreased in all cases. The RSPCHB is 6.5 rate focuses more slow in and 2 and additionally 2 circuits, yet in any case has a similar idleness as the PCFB.

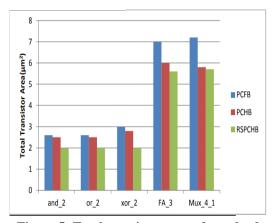

Figure 5: Total transistor area of standard circuits across PCFB, PCHB and RSPCHB templates

These circuits are more drowsy on the grounds that their draw down stacks were improved to sit tight for input legitimacy. In Figure 5 we see a differentiation between the general semiconductor region of the different reference plans. Captivating that the PCHB turns out to be more modest than the PCFB. The diminished intricacy of the semiconductor stacks in its information rail is to thank for this improvement by and by. By and large, 15.7% more modest than the PCHB layout and 20.3% more modest than the PCFB format. The half-process duration supposition makes impartiality distinguishing proof at the information simpler, prompting this result.

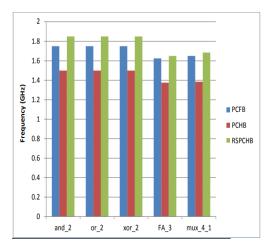

Figure 6. Frequency of standard circuits across PCFB, PCHB, and RSPCHB templates

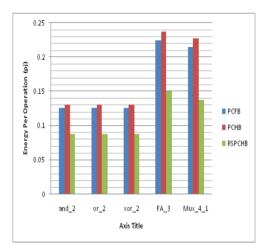

As can be seen in Figure 6, the HCFB template has a more noteworthy recurrence than the other four formats while utilizing any of the five standard circuits. By and large, 7.5% more frequently than the PCFB. The PCHB has a cycle time of 18 changes, the RSPCHB of 14, and the PCFB of 14. Conversely, the RSPCHB gives a more prominent recurrence in light of the fact that large numbers of its changes, outstandingly those that distinguish input lack of bias, are less muddled. This demonstrates that HCFB might accomplish similar recurrence as the PCFB while involving even less space and less semiconductors for these speedy advances. Figure 7 shows the detailed power utilization of commonplace circuits on a for each activity (or per-cycle) premise. Across each of the five rules, the RSPCHB layout has lower energy use than the PCFB and PCHB designs. When contrasted with the PCFB and PCHB formats, the RSPCHB design utilizes 30% and 34% less energy by and large. Given the enormous measure of room saved, the minor expansion in recurrence, and the little expansion in dormancy, this is fairly nice.

#### **Performance of Evaluation**

The HSpice e program is utilized to reproduce the circuits, and the model records utilize a 64.5 nm process. A capacitance of 4 fF/wire is associated with every hub that gives yield. This degree of capacitance is regular of short wires with this innovation, in light of the separated design. The doors are planned to such an extent that an inverter with a pmos width of 20 lambda units and a nmos width of 10 lambda units has a similar driving strength (lambda is characterized as a portion of the

base entryway length). All out scattered power is the reason for all power and energy computations.

ActaEnergetica

5. Figure 7: Energy per operation of standard circuits across PCFB, PCHB, and RSCHB templates.

#### II. CONCLUSION

Utilizing various predesigned layouts for asynchronous QDI circuits, we took a gander at probably the most straightforward MSI circuits. Leather treater is an electronic plan computerization apparatus that has been utilized to make and reenact rationale entryways and certain MSI circuits in these plans. The creator is sure that the recommended plan will act as an establishment for the improvement of high-speed, low-power computerized circuits such pipelined multipliers utilized in computerized signal handling uses, everything being equal.

#### REFERENCES

- Montek singh and steven M.Nowick The design of High performance dynamic asynchoronous pipelines; Lookahead style IEEE Transactions on Very Large Scale Integration systems.2007.

- Alain J. Martin ,Asynchronous Techniques for Systemon-Chip Design, Vol. 0018-9219\_2006.IEEE 94, No. 6, June 2006 , Proceedings of the IEEE.

- Sutherland and S. Fairbanks, "GasP: A Minimal FIFO Control," Proc. 7th Int'l Symp. Asynchronous Circuits and Systems (ASYNC 01), IEEE CS Press, 2001, pp. 46-53.

- A Lines, "Asynchronous Interconnect for Synchronous SoC Design," IEEE Micro, vol. 24, no. 1, 2004, pp. 32-41.

- A.M. Lines, Pipelined Asynchronous Circuits, tech. report no. CaltechCSTR: 1998.cs-tr-95-21, Dept. of Computer Science, California Inst. of Technology, 1998.

- M. Singh et al., "An Adaptively Pipelined Mixed Synchronous-Asynchronous Digital FIR Filter Chip Operating at 1.3 Gigahertz," IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 18, no. 7, 2010, pp. 1043-1056

- M. Singh and S.M. Nowick, "The Design of High Performance Dynamic Asynchronous Pipelines: High Capacity Style," IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 15, no. 11, 2007, pp. 1270-1283.

- P.A. Beerel and A. Xie, "Performance Analysis of Asynchronous Circuits Using Markov Chains," Proc. Concurrency and Hardware Design, LNCS 2549, Springer, 2002, pp. 313-344.

- G. Gill and M. Singh, "Automated Microarchitectural Exploration for Achieving Throughput Targets in Pipelined Asynchronous Systems," Proc. IEEE Symp. Asynchronous Circuits and Systems (ASYNC 10), IEEE CS Press, 2010, pp. 117-127.

- P. Prakash and A.J. Martin, "Slack Matching Quasi Delay-Insensitive Circuits," Proc. 12th IEEE Int'l Symp. Asynchronous Circuits and Systems (ASYNC 06), IEEE CS Press, 2006, pp. 195-204.

- B. Quinton, M. Greenstreet, and S. Wilton, "Practical Asynchronous Interconnect Network Design," IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 16, no. 5, 2008, pp. 579-588.

- M. Ferretti and P.A. Beerel, "High Performance Asynchronous Design Using Single-Track Full-Buffer Standard Cells," IEEE J. Solid-State Circuits, vol. 41, no. 6, 2006, pp. 1444-1454.

- G. Gill et al., "Low-Overhead Testing of Delay Faults in High-Speed Asynchronous Pipelines," Proc. 12th IEEE Int'l Symp. Asynchronous Circuits and Systems (ASYNC 06), IEEE CS Press, 2006, pp. 46-56.

- O.A. Petlin and S.B. Furber, "Scan Testing of Micro-pipelines," Proc. 13th IEEE VLSI Test Symp. (VTS 95), IEEE CS Press, 1995, pp. 296-301."

- T.E. Williams, "Self-Timed Rings and Their Application to Division," doctoral dissertation, Dept. of Electrical Eng., Stanford Univ., 1991.

- T.E. Williams and M.A. Horowitz, "A Zero-Overhead Self-Timed 160ns 54b CMOS Divider," IEEE J. Solid-State Circuits, vol. 26, no. 11, 1991, pp. 1651-1661.

- M.N. Horak et al., "A Low-Overhead Asynchronous Interconnection Network for GALS Chip Multiprocessors," IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, vol. 30, no. 4, 2011, pp. 494-507

- E. Beigne et al., "An Asynchronous NOC Architecture Providing Low Latency Service and Its Multi-level Design Framework," Proc. 11th

IEEE Int'l Symp. Asynchronous Circuits and Systems (ASYNC 05), IEEE CS Press, 2005, pp. 54-63.