# A Low Voltage Novel High-Performance Hybrid Full Adder for VLSI Circuit

# Jan Soliński

PhD, Polish Member Committee of the WEC, Warsaw, Poland

## Dr. Nitin Sherje

Associate Professor and Head of Department, Smt. Kashibai Navale College Of Engineering, Pune, India npsherje@sinhgad.edu

## **Keywords**

Power, Design, Adder, Logic, Supply.

# Abstract

In computerized CMOS design, power utilization has been a main pressing issue for a considerable length of time. This is on the grounds that exceptional IC manufacture innovation considers the utilization of nano-scale gadgets, which makes it hard to give power to circuits, forestall power spillage, or eliminate the intensity that these gadgets produce. Power utilization and slack time may both be diminished by adjusting the size of the semiconductors utilized in each stage. In this work, an assessment of complete adders that have effective boundaries like PDP, power, and postponement through power utilization and speed is introduced. These total adders are the result of an assortment of design endeavors. This article presents the design and execution of a crossover the slightest bit adder and the slightest bit subtractor. The CMOS (correlative metal oxide semiconductor) logic and pass semiconductor logic are both used in the structure of the cross breed adder circuit. As of late, the design has been extended to help both 16 and 32 bit information. To foster a full adder circuit that is more reasonable for the necessities of individuals living in the current regarding power, deferral, and region, it is important to assess the proposed full adder circuit against the regular adders that are as of now being used. In its ongoing execution, the 1-bit half and half adder utilizes EXNOR logic related to transmission entryway logic. The conscious fuse of exceptionally frail CMOS inverters combined areas of strength for with entryways prompted a postponement of 224 picoseconds and a typical power utilization of 4.1563 microwatts for a supply voltage of 1.8 volts. This brought about a postpone that was modestly low notwithstanding the incredibly low power utilization. Both the power and the deferral were estimated to be 1.17664 W and 91.3 ps when the supply voltage was 1.2V. The execution of the thought was finished utilizing the slightest bit, yet it can possibly be ventured into a 32-cycle design from here on out. When contrasted with the few full adder design types currently in presence, the arranged execution gives prevalent execution concerning both power and speed.

Received by the editor: 20.07.2022 Received in revised form: 09.10.2022 Accepted: 27.10.2022

#### 1. INTRODUCTION

To meet the requesting prerequisites of these future low-power and fast correspondence computerized signal handling chips, it is the ideal opportunity for us to examine the very much designed profound submicron CMOS advancements. The proficiency with which number-crunching circuits can complete confounded calculations like convolution, connection, and computerized separating is a significant figure deciding the degree of execution that might be accomplished by a wide assortment of utilizations, including computerized signal handling. In extremely huge scope combination (VLSI) frameworks, the circuits that are utilized the most often and widely are those that truly do quick number juggling calculations. These circuits incorporate adders and multipliers. Starting from the start of this long time, the semiconductor business has been observer to a transient ascent in the quantity of complex sight and sound based applications that are coordinated into portable electronic gadgets. Notwithstanding, the main thing to zero in on in this area is tracking down ways of eliminating the ascent in power utilization that happens once a specific

scope of working recurrence has been reached. Furthermore, because of the compact gadgets industry's brilliant ascent as far as both interest and allure, item designers are under expanding strain to foster gadgets that have a more modest silicon region, more prominent speed, longer battery duration, and greater reliability. The XOR and XNOR circuits are key parts that are utilized in a wide assortment of circuits, including yet not restricted to number-crunching circuits (adders and multipliers), blowers, comparators, equality checkers, code converters, blunder distinguishing or mistake revising codes, and stage locators. The adder is the fundamental part of cutting edge number juggling circuits, which incorporate tasks like as duplication, division, expansion, and exponentiation, among others.

## 2. LITERATURE REVIEW

Before, standard executions with an assortment of logic approaches have been used to make fulladder cells [1-4], and these equivalent executions are the thing are being utilized for correlation in this specific piece of exploration. Despite the fact that they all carry out a role that is practically identical to each other, how the go-between hubs are delivered and the quantity of semiconductors in each shifts. The different logical styles each tend to focus on a specific feature of execution over the others. A circuit's speed, size, and power dissemination, as well as the multifaceted nature of its wiring, are essentially impacted by the logic style that is used in logic doors. The postponement of the circuit is characterized by the quantity of reversal levels, the quantity of semiconductors associated in series, the extents of the semiconductors (at the end of the day, the channel widths), and the capacitances of the intracell wire. The quantity of semiconductors, their sizes, and the level of wiring multifaceted design are While some of them just utilize a solitary logic style all through the sum of the total adder, others utilize numerous logic styles while executing it. The exemplary reciprocal (CMOS) style-based adders (with 28 semiconductors) have various advantages, including their protection from voltage scaling and its capacity to scale in size, however they likewise have various downsides, including high information capacitance and the requirement for supports [5]. One more equivalent sort of savvy design is the mirror adder [6,] which has generally a similar power utilization and semiconductor count (as that of [5]), yet the greatest convey proliferation way/postpone inside the adder is extensively more limited contrasted with that of the regular CMOS full adder. Then again, CPL exhibits powerful voltage swing reclamation by the usage of 32 semiconductors [7-8]. Then again, CPL isn't the most ideal choice for applications that consume little power. The large number of semiconductors, static inverters, and data sources that are over-burden are the variables that keep this technique from working ideally. This is because of the great exchanging action of the mediator hubs, which builds the exchanging power. TGA, which just requires 20 semiconductors for full adder execution [9-10], had the option to appropriately conquer the essential downside of CPL, which was the voltage decay. In any case, the specialists are additionally worried about different deficiencies of CPL, like its unfortunate speed and over the top power utilization. Later on, scholastics focused their consideration on a strategy called crossover logic, which utilized the qualities of an assortment of logic styles to build the general exhibition. Vesterbacka [11-12] portrayed a 14-semiconductor complete adder that utilized numerous logic styles in its design and execution. Likewise, Zhang et al. [13] gave the cross breed pass-logic static CMOS yield drive full adder (HPSC). In this specific HPSC circuit, the XOR and XNOR capabilities were all the while created by pass semiconductor logic module by using just six semiconductors. These semiconductors were then utilized in CMOS module to deliver fullswing results of the full adder; nonetheless, this came to the detriment of expanded semiconductor count and diminished speed. Despite the way that crossover logic styles give promising execution, by far most of half breed logic adders have issues connected with unfortunate driving capacity, and their presentation endures extraordinarily in the flowed method of

factors that impact the general size of the circuit.

activity on the off chance that suitably designed supports are excluded from the design of the hardware.

## 3. DESIGN OF PROPOSED FULL ADDER

#### 3.1 CMOS Logic

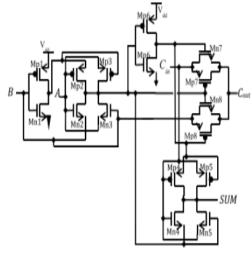

Full Adder Using CMOS to give full adder usefulness while keeping a low power utilization, a CMOS logic type is used. As a rule, they might be separated into two classifications: integral CMOS circuits and PTL circuits. Figure 1 shows a corresponding CMOS full adder that utilizes CMOS structure as its establishment. C-CMOS is profitable because of its versatility while scaling the voltage, as well as its capacity to scale the size of the semiconductors.

**Figure 1. Proposed Circuits**

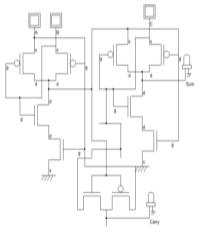

#### 3.2 Full Adder using PTL

PTL might be utilized to make a total adder by connecting the NMOS PTL with a MUX. This will permit the PTL to work as an adder. Because of the way that we don't involve PMOS pair to NMOS, it differs with TGA. As represented in Figure 2, it is feasible to make a total adder by utilizing PTL related to MUX logic, XOR logic, or XNOR logic. This diminishes the quantity of semiconductors expected as well as the postpone in yield.

Figure 2.Full adder using PTL

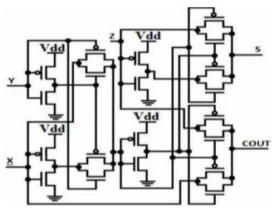

## 3.3 Transmission Gate Adder

The transmission door works in much the same way to a switch, showing low obstruction and capacitance, and keeping a DC trademark that is unaffected by the contribution (as found in Figure 3). In NMOS and PMOS semiconductors, separately, it connects the source terminals to the source terminals and the channel terminals to the channel terminals. Empower signals are utilized to turn on and off the two semiconductors simultaneously. At the point when a NMOS semiconductor is passing a '0' signal, it releases the result level with the goal that it is at nothing. Whenever a P type MOS semiconductor is conveying a '1' message, it charges the result so it is at a logic high.

Figure 3. Full Adder using Transmission Gate

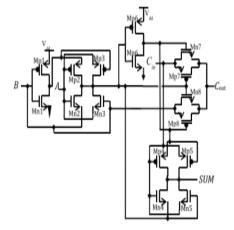

#### 3.4 Hybrid Logic Style

There are three modules: MOD1, MOD3, and MOD2. MOD1 and MOD3 are the EXNOR modules, which execute the Total result. MOD2, then again, is the convey age module, which is used to diminish idleness and produce short pathways. One of the two EXNOR modules is developed by utilizing PTL (2T), which assists with limiting the quantity of semiconductors as well as how much power that is utilized. Transmission entryways are utilized in the resulting execution of the EXNOR module (4T). Considering this, the in general 6T hardware that was made using EXNOR modules has a lower power utilization, furnishes the total result with a lower number of semiconductors, and works at a quick speed when contrasted with the conventional EXNOR module, as displayed in Figure 4. There are four semiconductors engaged with the execution of the convey age module. The information signal voyages by means of a solitary transmission door, which abbreviates the distance a convey signal should head out to arrive at its objective and eliminates the defer that it encounters.

Figure 4. Hybrid Full Adders

## 4. EXPERIMENTAL RESULTS

#### 4.1 Simulation Setup

The 1-digit complete adder that has been built is designed using three particular modules, with MOD1 and MOD2 being utilized for the improvement of the Total sign (Aggregate), and MOD3 being involved without anyone else for the age of the result Convey signal (Cout). The XNOR module is utilized in Modules 1 and 2, while the convey module is fabricated freely to streamline the circuit with regards to power, postponement, and chip region all in all. The XNOR module in this circuit is essentially liable for how much power that is consumed by the general adder circuit. Thus, the module has been created to consume as little power as is humanly useful. The circuit that was created utilizing a XNOR module for aggregate age is delineated beneath in figures 5, 6, and 7. By using the inverter channel that was developed, the power utilization of the XNOR circuit was diminished. Semiconductors Mp3 and Mn3 carry out the role of semiconductors and are liable for reestablishing the level, which guarantees that the result signals have going all out levels. The XOR and XNOR geographies, the two of which require four semiconductors, give an answer, in spite of the fact that they come to the detriment of a low logic swing. Then again, to accomplish predominant logic swing than that of a XOR/XNOR module with just four semiconductors, the XOR/XNOR module in utilizes six semiconductors. In contrast with the XOR/XNOR circuit, which utilizes six semiconductors, the XNOR gave in this task has a low power utilization and a high handling speed. The convey signal that is obtained at the result of the proposed circuit is achieved in the accompanying manner: The convey signal, meant by Cin, is communicated by the transmission entryway, which is made out of a determination of semiconductors, so shortening the general convey spread course. Moreover, the capability of transmission entryways is to guarantee a decline in the time it takes for a result sign to engender (Cout).

🔚 ActaEnergetica

Figure 6 Circuit design for 1-bit Full Adder

**Figure 5.Layout Design**

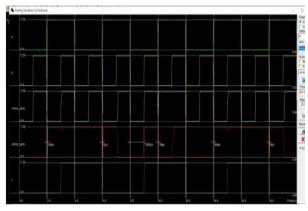

**Figure 7.Simulation Results**

## 4.2 Experimental Results

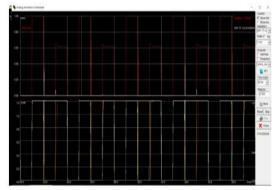

The accompanying table gives a plain portrayal of the discoveries of the investigations led on the reproduced adder and subtractor circuits depicted previously. An investigation into the deferral, semiconductor count, and how much power consumed gives an unmistakable picture that characterizes the circuit innovation that is better than the others by contrasting the power and postpone all alone, as delineated in Figures 8 and 9.

Figure 9. Frequency versus Time

## 4.3 Discussion of Results

The objective of this undertaking is to make a 1-bit Full Adder circuit utilizing 10, 14, and 20 semiconductors. The field of low power VLSI centers around lessening power scattering, supply voltage, spillage flows, and the region of the chip, as these are the basic models that should be dealt with. An elevated degree of a framework's reliability might be gotten by bringing down its expense, weight, and size, which can all be achieved by diminishing the complete number of semiconductors. In this way, a decrease in chip size can assist with accomplishing both a lower power utilization and a more modest space need. There are two strategies accessible for limiting circuits: the human strategy and the PC technique. The proposed project, a 1-digit crossover Full Adder, was executed utilizing the human strategy and comprised of 10, 14, and 20 semiconductors. Recreations were done. Eventually, the recreation study was contrasted with the customary Adder regarding power utilization, delay, and the result of region and power delay. As per the discoveries of the reenactment, we can express that the power postpone item (PDP), otherwise called how much energy consumed by the circuital design, will naturally increment with an expansion in the quantity of semiconductors, which is in opposition to the law administering low power frameworks. Moreover, we have fostered a 1-cycle Full Subtractor that uses 8, 15, and 20 semiconductors. In the domain of low power VLSI, the most fundamental factors that are stressed on are power scattering decrease, supply voltage decrease, spillage current decrease, and chip region decrease. It is feasible to upgrade the steadfastness of a framework while diminishing the expense, weight, and actual size of the framework, and this is achieved by decreasing the quantity of semiconductors in the framework. Thus, the power utilization and diminished region might be fulfilled by decreasing the size of the chip. There are two strategies accessible for limiting circuits: the human strategy and the PC technique. The proposed project, a 1-cycle mixture Full Adder, was executed utilizing the human method and comprised of 10, 14, and 20 semiconductors. Reproductions were completed. To wrap things up, the consequences of the reproduction study were diverged from those of a customary adder for power utilization, postponement, region, and power defer item. As indicated by the discoveries of the reenactment, we can state that as the quantity of semiconductors

expands, the power postpone item (PDP), otherwise called how much energy consumed by the circuital design, additionally increments naturally. This is the sort of thing that doesn't comply with the law of low power frameworks, which is shown in table1.

| Design    | Average  | Delay(Ps) | PDP    | No of       |

|-----------|----------|-----------|--------|-------------|

|           | Power    |           |        | transistors |

| 1-bit FA  | 0.533mW  | 45        | 23.985 | 16          |

| 10T FA    | 6.719µW  | 26        | 17.464 | 10          |

| 14T FA    | 11.054µW | 20        | 21.08  | 14          |

| 20T FA    | 0.255mW  | 10        | 1.02   | 20          |

| 24T FA    | 0.383mW  | 48        | 18.384 | 24          |

| 1-bit FS  | 2.935µW  | 7         | 20.545 | 14          |

| 14T FS    | 3.130µW  | 14        | 42.84  | 14          |

| 15T FS    | 1.661µW  | 20        | 33.22  | 15          |

| 2-bit FS  | 19.171µW | 25        | 14.275 | 24          |

| TGA       | 0.117µW  | 24        | 2.808  | 20          |

| Adiabatic | 8.094µW  | 14        | 13.316 | 15          |

#### TABLE1. POWER DISSIPATION OF DESIGNS

#### 5. CONCLUSION

Executing circuits utilizing different strategies takes into consideration the presentation examination of a low-power fast half breed full adder still up in the air. First and foremost, we fabricated an entire adder utilizing 10 semiconductors, where the power and postponement of this still up in the air. The primary activity was rehashed with 14 semiconductors, and afterward with 20 semiconductors; the power defer not entirely set in stone after every one of these emphasess. Subsequent to putting the recommended half and half circuit through its speeds, indistinguishable estimations are completed to independently assess the results. The second period of this undertaking comprised of the real execution of the entire Subtractor circuit, which incorporated a sum of 8 semiconductors, 15 semiconductors, 20 semiconductors, and the recommended circuit. Precisely the same discoveries have been contrasted and each other all in all, and with the utilization of timing graphs, we have had the option to get values for power and deferral. The development of a total adder utilizing DSCH2 and Microwind instruments was the focal point of this undertaking. The power scattering, idleness, and design region of the proposed cross breed circuit were estimated and contrasted with those of the current circuits. These estimations were reliant upon the size of the semiconductors. At the point when a similar task is completed in either guide illustrations or rhythm

devices, it is noticed that the reproduction results are unrivaled. This is the situation while thinking about the exact power utilization and defer settings. The size of the semiconductors plays a part in deciding the region of the circuit too.

#### References

- N. Weste and K. Eshraghian, Principles of CMOS VLSI Design: A System Perspective, Addison-Wesley, Reading, Mass, USA, 1993.

- J. P. Uyemura, Introduction to VLSI Circuits and Systems, John Wiley & Sons, New York, NY, USA, 2002.

- S.-M. Kang and Y. Leblebici, CMOS Digital Integrated Circuits: Analysis and Design, Tata McGraw-Hill, New York, NY, USA, 2003.

- 4. N. Weste and D. Harris, CMOS VLSI Design, Pearson Wesley, 2005.

- N. H. E. Weste, D. Harris, and A. Banerjee, CMOS VLSI Design: A Circuits and Systems Perspective, 3rd ed. Delhi, India: Pearson Education, 2006.

- J. M. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2nd ed. Delhi, India: Pearson Education, 2003.

- D. Radhakrishnan, "Low-voltage low-power CMOS full adder," IEE Proc.-Circuits Devices Syst., vol. 148, no. 1, pp. 19–24, Feb. 2001.

- R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, no. 7, pp. 1079–1090, Jul. 1997.

- C. H. Chang, J. M. Gu, and M. Zhang, "A review of 0.18-μm full adder performances for tree structured arithmetic circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 686–695, Jun. 2005.

- A M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 10, no. 1, pp. 20–29, Feb. 2002.

- M. L. Aranda, R. Báez, and O. G. Diaz, "Hybrid adders for high-speed arithmetic circuits: A comparison," in Proc. 7th IEEE Int. Conf. Elect. Eng. Comput. Sci. Autom. Control (CCE), Tuxtla Gutierrez, NM, USA, Sep. 2010, pp. 546–549.

- M. Vesterbacka, "A 14-transistor CMOS full adder with full voltageswing nodes," in Proc. IEEE Workshop Signal Process. Syst. (SiPS), Taipei, Taiwan, Oct. 1999, pp. 713–722. [

- M. Zhang, J. Gu, and C.-H. Chang, "A novel hybrid pass logic with static CMOS output drive full-adder cell," in Proc. Int. Symp. Circuits Syst., May 2003, pp. 317–320.