# Architecture Modelling of MOS Device for the Circuit simulation

# Louis Jestin

Adjunct Professor, The University of Cape Town, Rondebosch, RSA

# Ibrahim Hamdan

Department of Electrical Engineering, Faculty of Engineering, South Valley University, Egypt

# **Keywords**

Metal-Oxide-Semiconductor

# Abstract

Throughout the course of recent years, the Metal-Oxide-Semiconductor Field Impact Semiconductor (MOSFET) has been the essential part of coordinated circuits. With the advancement of innovation, numerous MOSFET structures with channel lengths of 0.1 pm or less have been recorded in modern examination. The gadget material science and plan tradeoffs among MOSFET's boundaries can be better perceived by looking at these state of the art gadget designs one next to the other. In this review, we think about gadgets utilizing exploratory information, gadget recreation, and logical displaying. The gadgets were made in various different examination offices. Insightful models resolving issues like limit voltage, short-channel impact, and immersion current for these different MOSFET geographies are made under the direction of reenactments and trial information. Then, to look at the gadgets genuinely, these insightful models are utilized to streamline every gadget's underlying boundaries. The main plan components are stressed, and the benefits and detriments of every gadget structure as far as a few execution regions are investigated.

Received by the editor: 20.03.2022 Received in revised form: 05.06.2022 Accepted: 24.06.2022

### 1. INTRODUCTION

Throughout recent years, the MOSFET (METAL-**OXIDE-SEMICONDUCTOR** Field Impact Semiconductor) has been the essential part of coordinated circuits. Silicon MOSFET based VLSI circuits have persistently expanded execution and additionally diminished costs for semiconductor chips for information handling and memory activities on account of innovative progressions and the high versatility of the gadget structure. Modern exploration has recently centered around MOSFETs with channel lengths of 0.1 pm and beneath; the drivers for additional scaling are higher speed and thickness as well as lower power necessities for incorporating a full framework on a chip [I]. In the writing, various 0.1 pm MOSFET gadget designs have been recorded. The principal proposed gadget

designs ought to be differentiated one next to the other under similar arrangement of imperatives in light of the fact that every gadget structure enjoys benefits and detriments. Be that as it may, on the grounds that there are so many compromises between MOSFET's properties, directing a comprehensive gadget comparison is troublesome. For example, looking at ring oscillator speed information for MOSFETs with equivalent channel lengths yet contrasting limit voltages or fluctuating levels of short-channel effect can be totally illogical.

Gadget reenactment is a helpful instrument for contrasting various gadgets [2] however provided that the test system is adjusted to work with genuine gadgets; in any case, the outcomes are sketchy. Insightful models offer helpful actual comprehension. In this review, we think about

gadgets utilizing trial information, gadget reenactment, and logical displaying. The gadgets were made in various different examination offices. Information from reenactments and examinations act as significant aides for the production of logical models. Gadget test systems are utilized to extrapolate the current data. Then, to look at different gadget structures genuinely under similar arrangement of limitations, the logical models are used to upgrade every gadget structure. These MOSFET contraptions were utilized in this examination:

- MOSFET with uniformly doped substrate (UD);

- Delta-doped MOSFET (DD);

- Pocket-implanted MOSFET (PI);

- Partially-depleted SO1 MOSFET (PDSOI);

- Fully-depleted SO1 MOSFET (FDSOI);

- Dynamic-threshold MOSFET (DT);

- and Double-gate MOSFET (DG)

The DD MOSFETs that were utilized in this examination were made. The DT MOSFET involves a similar body contact setup as in [8]. DG MOSFETs are made by [9]. The summed up expansions of the gadgets referenced above incorporate more MOSFET structure types. For example, DD MOSFET can likewise address MOSFETs with retrograded doping channels that utilization particle implantation and nuclear layer doping [4]. Radiance doping is likewise addressed by PI MOSFET [12]. The encompassing door MOSFET [IO] and the DELTA MOSFET [1 I] are similarly addressed by DG MOSFET. It ought to be noticed that despite the fact that while MOSFET fabricated with the methodology standard utilizing particle implantation don't have uniform channel doping profile, we use the consistently doped channel MOSFET to mirror a more regular plan than deltadoping and to improve on examination.

#### A. Cryo-Mos Transistor Modeling

A semiempirical procedure was utilized to explicitly configuration low-temperature circuits for rocket [19], [20], logical device [21], ultralow-commotion indicators [22], cryobiology [23], and different applications. With this technique, model boundaries should be separated through tedious and exorbitant low-temperature perceptions to change RT smaller models to the ideal low temperature [22], [24], [25]. To represent cryogenic working down to 4.2 K [28]- [30], experimental temperature-scaling conditions have been acquainted with the RT physical science based MOS semiconductor model [26], [27]. The contrast between the deliberate subthreshold swing (SS) an incentive for a long gadget at 4.2 K (10 mV/decade) and the hypothetical warm cutoff UT ln 10 (0.8 mV/decade) demonstrates that something more essential is absent. We will show that key lowtemperature actual peculiarities such point of interaction catching and fragmented ionization [34, 35] have not been enough considered so far. Moreover, under 10 K, the characteristic transporter fixation, ni, shows very low qualities, prompting number juggling sub-current in carried out logical equations or assembly issues in PC supported plan reproductions. In this way, the cryogenic balance condition in mass semiconductors more than 10 K is the main subject shrouded in standard references on semiconductor gadgets [26], [27], and [39]. Beginning from the Poisson condition at low temperature, insightful gadget material science models leave an opening between the 0 K estimation and 77 K unfilled. In this exploration, we create a science completely material based MOS semiconductor model that can be utilized to foresee MOS semiconductor conduct from room temperature to profound cryogenic temperatures. We start by affirming the Boltzmann measurements' persistent appropriateness down to the profound cryogenic zone.

# B. Fabrication and Characterization of Semiconductor Memristor

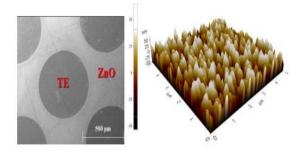

To make the SiO2 substrate required for gadget creation, a standard RCA cleaned p++ Si wafer was oxidized for 30 minutes at 1050 °C under a dry O2 stream pace of 10 sccm. Utilizing a metallic Zn target and an Ar and O2 gas stream, the ZnO dainty film was created by DC receptive magnetron faltering as a functioning 300 nm layer. The chamber's base tension was under 2 Torr, and the Ar to O2 proportion was 20:1. The method incorporated no warming of the substrates, and the faltering voltage was - 350 VDC. The INFICON XTM/2 estimated film thickness. For crystallization, the ZnO/SiO2/p++Si tests were toughened at 700 °C for 30 min in an Ar climate, and afterward utilized for X-beam powder diffraction (XRD) review. XRD examination was utilized to explore the ZnO design's crystallization using the GNR-APD 2000 Ace, 0.154 nm Cu-K radiation, and 2 points somewhere in the range of  $20^{\circ}$  and  $60^{\circ}$  at room

temperature. In Fig. 1a, the XRD designs are shown. With a hexagonal wurtzite structure, the ZnO flimsy movie has filled specially toward (002). The XRD design matches the ICSD 01-075-0576 detail.

# Fig. 1. a) Surface morphology AFM image of the ZnO; b) SEM surface image of the device displaying TE pattern (left); and (c) XRD pattern of the ZnO structure (right).

Under vacuum settings of under 10-6 Torr, aluminum was utilized to truly fume affidavit (PVD) metalize the base anode (BE) and top cathode (TE). By using a shadow cover with 500 m-width openings, the TE was metallized. Utilizing the FEI Quanta 450 in high vacuum at 20 kV, a filtering electron microscopy (SEM) picture of the memristor gadget's surface was caught (Figure 1(b), upper). The ZnO surface's AFM picture is found in (Fig. 1b, lower). The picture incorporates 512 x 512 pixels, the sweep region was 5 x 5 m2, and the output recurrence was 0.44 Hz. The surface was delivered reliably, as proven by the surface harshness factor (Ra) estimation of 0.044 m. Utilizing a test station and extraordinarily made memristor portrayal programming, the Keithley 2400 SourceMeter® was utilized to test the gadget's (I-V-t) memristive way of behaving at encompassing temperature. For this gadget, the consistence current was set at 300 A to keep hurt from overabundance current. Clearing the voltage between - 0.7V and +0.7V empowered the gadget to display memristive action.

#### C. Structures of Different Power MOSFET Devices

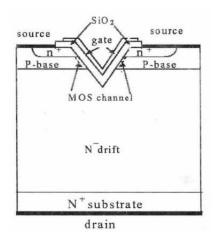

#### VMOS transistor (V groove)

A part of the VMOS or (V notch) semiconductor is displayed in Fig. 2. It is produced using a sort n' silicon epilayer with a p-layer diffused across the surface. A similar window is likewise utilized for the dispersion zones n'. In the focal point of the diffused n: zones, grooves (V's) are opened because of substance assault on the silicon. This Angular shape is made by utilizing hydrazine to draw silicon through windows in an oxide. The entryway is comprised of sides of V that have been thermally oxidized and in this manner metalized. Furthermore metallized is the source contact, causing a short out in the n and p "dispersions. The channel is situated on the gadget's lower side. This kind of semiconductor has the advantage of being clear and having its mathematical boundaries, especially the channel length, unequivocally controlled. The ongoing capacity is multiplied and the surface region is diminished by delivering two directs in each score. The n float zone's presence brings about a high voltage limit. These semiconductors might work in the VHF locale and have quick exchanging times. Since the direct in VMOS is built on the "Evil" plane, it has a lower surface versatility than VDMOS. The VMOS gadgets are not presently utilized since the compound scratching technique expected to make the V depression leaves numerous sodium particles on the carved surface, whose presence causes a ton of unwavering quality worries ".

#### Fig. 2-Schematic design of a V-groove MOSFET (VMOSFET). Structure shown represents one cell of the device

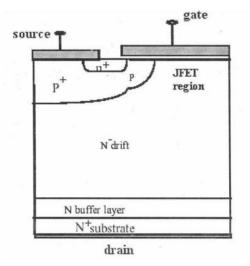

VDMOS transistor

The upward twofold diffused (VDMOS) semiconductor is right now the most generally utilized power MOSFET structure, as found in Fig. 3. To diminish the mass part of the channel obstruction, it starts with a n-type substrate that has been exceptionally doped. What's more, a n' epi layer is created, and two successive disseminations are made — one into the p-zone, where the source will be characterized by a suitable inclination, and the other into the n' epi layer. Following the development of the phosphorous-doped polysilicon,

slim, excellent door oxide is next shaped, framing the entryway. While the whole lower part of the wafer connects for the channel, contact windows are opened on top to characterize the source and door terminals. At the point when the door isn't one-sided, the p-zone isolates the n+ source from the n+ channel, and no ongoing streams (semiconductor is switched off). The minority transporters (electrons) in the p-zone are attracted to the region underneath the entryway plate when the door inclination is positive. As the inclination rises, more electrons are gotten into this limited region; thus, the neighborhood minority fixation outperforms the opening (P) focus and reversal happens. Current can now stream since a n divert has framed in the p material straightforwardly underneath the entryway structure, connecting the source to the channel. The entryway inclination directs how much current streams from the source to the channel.

### Fig-3 Schematic design of a VDMOSFET (DMOS) transistor. Structure shown represents half cell of the device

The power MOSFET is just a construction comprised of a few equal associated cells like those found in Fig. 2. The comparing opposition is.L/n-th of the single cell's RDS(ON), very much like with any resembling of indistinguishable resistors. The on-opposition of a bigger kick the bucket is lower, however it likewise has more prominent parasitic capacitances and less viable exchanging. For example, a 240-mie chip from Intersil has more north of 25,000 cells, while a 120-mif chip has around 5,000 cells. The difficulties with the superjunction (SJ) MOSFET incited the advancement of the semisuperjunction (SJ) MOSFET plan idea. This plan associates a better n-type layer to the lower part of the SJ structure. The base help layer is one more name for this n-float layer (BAL). The BAL doping fixation and thickness are essential plan factors in the semi-SJ structure. To dispose of one turn of the epitaxial development process, it has been exhibited that the semi-SJ MOSFET with the perspective proportion of four has a similar on-obstruction as the SJMOSFET with the viewpoint proportion of five.

Trench power MOSFET

The power MOSFET industry changed to channel entryway innovation around quite a while back "to bring down the opposition. The chaimel is made on the upward sidewalls of a channel that is scratched into the silicon surface in the channel door structure. otherwise called the UMOSFET . The JFET opposition is taken out because of the channel source current's upward course. This empowers evacuation of the on-obstruction notwithstanding b),' decline "of a part of the opposition. Moreover, by allowing a more modest cell "I'size extends the channel's thickness. Tragically, the planar DMOS method is more affordable than the channel door process. Moreover, the business should address dependability issues welcomed on by high electric fields at channel corners, which should be settled by adjusting the sides of the channels and lessening the electric field's force "utilizing the p" areas. Also, the expanded coupling between the channel and the entryway because of the augmentation of the door into the float zone brings about higher Mill operator capacitance and entryway charge, which can adversely influence exchanging execution. Like VMOS, channel MOSFET has a depression that is opposite to the surface, making a channel structure on the 1L0 plane ". Sharp edges can make a gadget breakdown, consequently they are just used in low voltage, high current applications. The planar gadget is more straightforward to build, however the channel method enjoys the benefit of having a higher cell thickness.

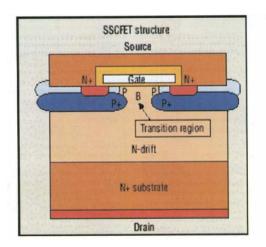

SSCFET and JBSFET

Silicon Semiconductor Corp., USA, reengineered the planar power MOSFET construction to acquire execution that is better than that of state of the art channel gadgets. Dependability troubles are diminished by keeping a planar design, which keeps

Semi-superjunction MOSFET

the manufacture interaction viable with normal CMOS process lines. Moreover, this engineering has made it conceivable to utilize a silicided entryway stack to bring down the MOSFET's inward door obstruction.

A profound p" locale in the SSCFETIO (Silicon Semiconductor Corp. FET) structure is self-adjusted to the door locale II. The progress zone, which lies beneath the door district, is utilized to shape an expected hindrance because of its higher doping focus and more profound expansion in both the vertical and horizontal headings. To further develop power MOSFET execution, the door width and change district doping profile are tuned. Shortening the channel length to diminish obstruction commitment is conceivable without agonizing over reach-through-incited breakdown since the door area at B (Fig. 4) is protected from the channel potential. Explicit on-protections for SSCFETs can move toward those accomplished in run of the mill channel power MOSFETs because of a channel commitment that is diminished to a portion of that seen in commonplace VDMOSFETs.

■ Superjunction (SJ)I COOLMOS<sup>TM</sup> transistors

Superjunction'V" (SJ MOSFET) ICOOLMOSTM have as of late made it practical to accomplish quicker speeds and more noteworthy breakdown voltages all the while. the superjunction's construction.

Fig. 4 - SSCFET device structure

In 1824, Jns Jacob Berzelius, a Swedish physicist, made the underlying revelation of the Si-C bonds. Eugene G. Acheson of Monongahela, Pennsylvania, made the primary SiC in the USA 67 years after the fact. By running an ongoing through a carbon pole that was lowered in the combination, he had the option to dissolve a mass of carbon and aluminum silicate. This examination created SiC gems with a dazzling blue color. Eugene named the new precious stone "carborundum" in light of the name Al2O3 - 11 "corundum," expecting a compound of carbon and aluminum. Afterward, he found that it was a silicon and carbon compound. In any case, it is as yet alluded to as "carborundum" wherever on the planet.

The first SiC item, a light emanating diode (Drove), was made in 1907. A more reliable and predominant innovation for SiC gem arrangement required a significant stretch of time to create. In 1955 [10], Lely et al. fostered a more satisfactory idea for creating SiC gems of prevalent quality. At the same time with the improvement of silicon innovation came propels in silicon material handling. Accordingly, there was little SiC research done in the thirty years that followed.

# 3. EXPERIMENTAL RESULTS AND DISCUSSION

Devices made utilizing a 28-nm mass CMOS innovation were exposed to RT and cryogenic testing. Past reports on the whole assortment of estimations, the estimation arrangement, and the portrayal can be found in [3] and [31]. Utilizing a dipstick, the examples were lowered into fluid helium (4.2 K) and fluid nitrogen (77 K) showers in the wake of being estimated at room temperature. This differentiations the model's expectations with estimations of straight exchange qualities (VDB = 20 mV) made on a long nMOS gadget with W/L = 3m/1 m in both the direct and logarithmic scales at RT and 4.2 K. The model's removed 0 qualities are reliable with the portrayal done in [31]. researches the effect of portability, interface traps, and inadequate ionization on the ebb and flow at 4.2 K. It ought to be noticed that connection point traps can make the SS decline to 10 mV/decade, and fragmented ionization brings down the edge voltage.

| VBG | MEASURMENT |

|-----|------------|

|     | MODEL      |

| 0.2 | 0.23 |

|-----|------|

| 0.3 | 0.13 |

| 0.4 | 0.26 |

| 0.5 | 0.28 |

| 0.6 | 0.32 |

| 0.7 | 0.44 |

| 0.8 | 0.52 |

The ON-state current at 4.2 K builds because of the critical expansion in portability. utilizes estimations made at RT, 77 K, and 4.2 K on a long pMOS gadget with W/L = 3 m/1 m on the straight and logarithmic scales to confirm the model for the ongoing in immersion (|VDB| = 0.9 V). As per the change in the EF-position, the distinction in the work capability between the metal and semiconductors, or ms, ascends in outright worth at lower temperatures.

#### A. Subthreshold-Swing Derivation

This part fosters an equation for the SS that records for temperature-subordinate connection point catching and deficient ionization. The incorporation of inadequate ionization shows the insignificant effect on SS. As far as possible, UT ln 10, recently found on lengthy devices [3], [31], can be acquired with the SS-offset of 10 mV/ten years above on account of the temperature reliance of point of interaction trap occupation, fs(Et). The standard method for communicating the SS is as nUT ln 10, where the slant factor, n, which depicts the takeoff from as far as possible, is given as (VGB/s). Under the assumption that fs(Et) from (13) is 1, (VGB/s) brings about 1 + (2q NAsi)1/2/[Cox(2 s b)]+q Nit/Cox [26], [51]. To represent a SS of 10 mV/decade, a gigantic Nit esteem on the request for 1013 cm2 is recovered at 4.2 K, expecting the best doping esteem underneath as far as possible, since Nit is duplicated by UT in this articulation. It ought to be anxious, in any case, that the temperature reliance of connection point trap occupation isn't considered in the given articulation for SS. The subthreshold slant, still up in the air by depending on float dissemination transport in the straight area and it is autonomous to expect that VGB.

ActaEnergetica

$$SS^{-1} = \frac{1}{\ln 10} \frac{1}{Qm} \frac{\partial Qm}{Qm} \frac{\partial \psi s}{\partial VGB}$$

The factor  $(1/Qm)(\partial Qm/\partial \psi s)$  is found from (12) by considering Qm Q f or Qsc  $\approx$  Q f in the subthreshold region.

#### CONCLUSION

A hypothetical MOS semiconductor model is made that is precise from surrounding temperature to the temperature of fluid helium. The model integrates deficient ionization, interface traps, bandgap temperature reliance, and versatility decrease. It depends on the Boltzmann measurements and has been demonstrated in the breaking point to 0 K. It is shown that deficient ionization protects a semiconductor's nondegeneracy at profound cryogenic temperatures and makes the edge voltage fall notwithstanding the general increment welcomed on by Fermi-Dirac circulation scaling. The SS is decreased to 4.2 K by the Fermi-Dirac temperature reliance of point of interaction trap occupation. It is feasible to foster a recipe for the SS that considers fractional ionization and temperaturesubordinate point of interaction catching. The recommended approach makes the significant actual structure for impending low-temperature CMOS circuit design.

#### **FUTURE WORK**

The focal point of the ongoing work is on dissecting Underlap-FinFET and TFET execution in the simple, RF, and NQS systems. This proposal's principal objectives are to improve Underlap-FinFET execution and cause to notice Germanium Passage FET's striking attributes. The effect of underlying change and fluctuation related issues in devices on gadget and circuit reliability has likewise been examined. Various expansions to these issues could be attempted as a feature of progressing research. Following are a few specific future extensions in light of the ongoing work:

1. In TFETs, BTBT for the most part occurs at the source/channel body intersection, where the entryway source and channel source voltages essentially affect the electric field. To enough explore gadget execution, it is urgent to think about

the sidelong expansion at the source/channel body intersection. Given the sidelong augmentation of the source/channel doping into the channel, the ongoing investigation can be actually extended to the conservative displaying of TFET.

2. Future examination can look at what trap charges mean for NQS execution for Underlap-FinFET and Germanium Passage FET.

The fundamental wellsprings of commotion in a simple IC's general clamor execution are MOSFETs. The fundamental issue for RF execution is clamor in a MOSFET's door voltage or channel current. The channel gleam clamor (1/f) and warm commotion impact the MOSFET commotion conduct the most. Considering that the overall clamor range thickness is conversely corresponding to door region, the 1/f commotion of the scaled devices has altogether expanded. 1/f regularly results from changes in portability or the general amount of charge transporters. For profound submicron devices, the effect of versatility changes on the 1/f commotion is more significant. Thusly, to show up at a summed up observational equation, the commotion qualities of the Germanium-TFET should be approximated by means of minimal displaying.

#### REFERENCES

- Baliga B J, Modern Power devices, (Wiley-Eastern, New York) 1987.

- 2. Grant D A & Gowar J, Power MOSFETs: Theory and applications, (Wiley, New York) 1989.

- Baliga B J, Power Semiconductor Devices, (PWS Publishing Co, Boston) 1996.

- 4. Intersil Application Note AN7244, October 1999.

- 5. Park I Y, Choi Y I, Chung S K, et al., Microelectron Journal, 32 (2001) 497.

- 6. Uesugi T, Kodama M, Kawaji S, et al., Proc IEEE ISPSD, 1998, p. 57.

- Chang H R & Holroyd F W, Solid State Electron, 33 (1990) 381.

- Zeng J, Mawby P A, Towers M S & Board K, Solid State Electron, 38 (1995) 821.

- K. Shenai, IEEE Trans on Electron Devices, 39 (1992) 1435.

- Baliga B J & Girdhar D A, Power Electronics Tech, 9 (2003) 24.

- 11. BaJiga B J, US Patent Application Publication No. US 2002/0177277 Ai, November 28,2002.

- 12. BaJiga B J, IEEE Electron Device Leu,S (1984) 194.

- Mehrotra M & Baliga B J, IEEE Trans on Electron Devices, 41 (1994) 1655.

- 14. Fujihira T, Jpn J Appl Phy, 36 (1997) 6254.

- Fujihira T & Miyaska Y, Proc IEEE ISPSD, 1998, p.423.