# Analytical Approach of Laboratory for the Microelectronics Fabrication

# **Anatoliy Goncharuk**

Professor, The International Humanitarian University, Odessa, Ukraine

# Ahmed F. Mohamed

College of Engineering and Islamic Architecture, Umm Al-Qura University, Makkah, Saudi Arabia

# Keywords

CMOS, Microelectronics Fabrication, MOSFET process, Microelectronics technology

# Abstract

We describe changes applied to a laboratory course in CMOS (Complementary Metal Oxide Semiconductor) fabrication to improve student learning and student impact (enrolment). The three most important course enhancements are as follows: 1) the use of a 2-mask MOS process, which significantly decreased the time it took students to design, fabricate, and verify the electrical properties of a MOSFET process; 2) the students' use of a semi-custom IC design, which significantly decreased the average design and processing time of previous years; and 3) the creation and implementation of a system of course prerequisites, which allowed a greater number of students to enrol in the course.

Received by the editor: 18.03.2022 Received in revised form: 03.06.2022 Accepted: 22.06.2022

## 1. INTRODUCTION

The foundation of many significant fields of science and business is microfabrication. It plays a crucial role in nanotechnology and is essential for the development of electrical devices. It is also directly connected to MEMS. It is essential that undergraduates have an introduction to the fundamental ideas of microfabrication. If the student has the chance to understand the principles while also being exposed to the real microfabrication procedures in a hands-on laboratory setting, the learning experience will be improved. This kind of lab will be helpful for future engineering careers and training, but it will also spark interest in graduate work in the domains of microelectronics and microfabrication. Microfabrication courses for undergraduates have been effectively incorporated into the curricula of several higher education institutions. These programmes all have a laboratory component where students can practise the

theoretical concepts they have learnt in class. A well-rounded engineer or scientist is produced as a result of this practical experience, which also improves comprehension of the underlying problems. The engineers who complete this experience are also better equipped to address the needs of both research and industry.

Microelectronics technology has significantly enhanced the capabilities of computers and communications systems, as well as fostering the development of whole new applications, such as personal computers. Microelectronics has become the linchpin of information technology due to its rapid growth and ability to provide ever-morepowerful and affordable instruments for manipulating electronic signals. It is fundamental to the following:

- computers, ranging from supercomputers to commercial computers to affordable home computers;

- communication systems, such as satellite communications and switching stations;

- consumer goods including pocket calculators, electronic watches, and video games;

The technology has experienced such rapid growth that commentators have dubbed it the microelectronics revolution. This revolution has been mostly brought about by the downsizing of circuitry, which results in devices that function faster and better. The cost of electronic equipment has decreased, their performance has increased, and their reliability has increased. Integrated circuit (IC) technology has advanced significantly since its conception by any metric, including cost for a specific purpose, circuit complexity, and performance. Gordon E. Moore anticipated that the number of parts on a chip would increase every year as it had done from the start of that decade in 1964. Twenty years later, Moore's rule still holds true for technology. Over the following 10 to 20 years, experts expect the trend to slow.

IC design will start to change how system engineers use ICs at the same time. The end user has far more flexibility when developing chips for a particular application because to new capabilities made possible by design software, silicon foundries, and the networks that connect them. The industry will be impacted by this trend and developments in fabrication technology.

## A. Microelectronic laboratory

The objective of the Nanoptronics Foundation is to further develop microelectronics science, innovation, and schooling by offering assets that help multidisciplinary review and examination.

The microelectronics community is very much positioned to offer fundamental offices and assets to help the schooling of first rate understudies and celebrated research staff.

Techniques utilized in the development of semiconductor devices: hypothetical and useful angles. This middle examinations compound fume statement and dissemination techniques, state of the art pollution control ideas, deformity free handling, and complete portrayal, including intersection entrance, resistivity, and oxide thickness. It likewise concentrates on exchanging speed, intersection qualities, spillage and gain, particle implantation, and strategy for fabrication.

# 2. LITERATURE REVIEW

(DZIEDZIC, A. 2001) Hidradenitis suppurativa (HS) is an ongoing, incendiary and excruciating skin infection that frequently unfavorably influences patients' personal satisfaction. Dermatology-explicit apparatuses, for example, the Dermatology Life Quality Record and Skindex are ordinarily used to survey personal satisfaction in patients with HS. Be that as it may, because of the absence of explicit inquiries, these scales may not be suitable and reflect genuine issues. OBJECTIVE: Interpretation and approval of the Clean adaptation of recently evolved HS-explicit polls - Hidradenitis suppurativa personal satisfaction (HiSQOL). MATERIALS AND Techniques: From the first English adaptation of the polls, forward and in reverse interpretations into Clean were made by worldwide guidelines. Approval was performed on a gathering of 30 HS patients who finished the poll two times, 4-5 days separated.

(ROOS-KOZEL,1984) This white paper depicts how RFID labels, particularly recieving wires for the HF band (13.56 MHz), can be fabricated from modest adaptable substrates. Physico-compound, mathematical, DC and AC electrical properties, as well as long haul steadiness (under warm, mugginess warm and mechanical pressure) are different on various paper or foil substrates. Obstruction estimations during relieving were utilized to concentrate on the polymerization rate, which is vital for expanding process limit.

(DE FOSSE, S. F., WILLIAMS, 1985) Alludes to a remote distinguishing proof framework in view of radio recurrence transmission. Such frameworks comprise of a fixed handset, called a peruser, and a versatile handset and radio wire, regularly called a RFID tag or transponder (either incorporated with the tag or independent). Today, RF labels comprise of small recieving wires inserted straightforwardly into CPUs. There are two sorts of RFID labels: dynamic (utilizing a battery to drive them) and inactive (utilizing energy prompted at the recieving wire terminals). RFID frameworks work at different frequencies from 125 kHz to 5.8 GHz. Correspondence range essentially relies upon working recurrence

(DOBKIN, D. M.2008) A novel and smaller planar UHF RFID tag with broadband activity and further developed read range is introduced. The design of the label comprises of a T-coordinated dipole radio wire with a three-sided her SRR cluster organized symmetrically on the arm. A three-sided SRR arm mounted on the construction gives the conservativeness and magnificent impedance matching expected to boost read range. Estimation results show that the arranged tag has a most extreme perused scope of 9.6 meters in the European UHF RFID band at 866 MHz and essentially better read range in other UHF RFID groups in the 860-930 MHz range. increment. Contrasts in read ranges estimated in azimuth and rise ranges are additionally recommended.

(REDINGER, D., MOLESA 2009) Enormous scope RFID transmissions are ordinarily restricted to the close to field at low power levels (in the scope of a couple of centimeters to around 30 cm; such frameworks use circle recieving wires) where the majority of the energy produced by the peruser is , happen around 135 kHz and 13.56 MHz. with pioneer and tag). The working reach at higher working frequencies, particularly 860/960 MHz and 2.4-2.5 GHz, is in the scope of a few meters, and RFID labels working at these frequencies require a dipole.

(ROGERS, J. A. 2004) PDMS replication is typically thought to be solid at all scales down to the nanoscale, however to additional help this generally acknowledged view, there is a requirement for An itemized quantitative correlation of is as yet required. Here we show that the top surface of a centimeter cubic PDMS block collapsed onto an inflexible plate veers off from the normal levelness, with the plentifulness of deviation relying upon the crosslinking convention. As a useful arrangement, we recognize a reasonable two-step convention that kills these replication blunders. We utilize limited component recreations to show that the impact emerges from warm compression as the example cools from the restoring temperature to the functioning temperature.

## 3. EXPERIMENTAL

We had our understudies configuration utilizing the Athena process simulation device and develop a clear two-cover semiconductor gadget process in the lab to give them the potential chance to configuration, construct, and test a full semiconductor process (and consequently help understudy proprietorship). The two-cover NMOS semiconductor, the two-veil PMOS semiconductor, or the sun powered cell method were the choices accessible to the understudies. Since the two-cover MOS method just required two photolithography processes and contained three layers - dispersion, oxide, and metal — it was picked. The aluminum gate[3], turn on glass as a dopant source, and an entryway that covers the source and channel were the underpinning of the two-veil NMOS or PMOS innovation. The 2-veil method, which was far less difficult than the 7-cover CMOS beforehand being used, saved 40 minutes each run during simulation. The 2-veil fabrication process took less time in the lab than the 7-cover fabrication process by no less than about two months. The understudies utilized the time saved to completely test and examine the made devices more. For example, the understudies had the option to utilize the SPC information they had procured while monitoring the arrangement device's enlistment mix-up to ensure a 95% circuit yield. We ask the right now selected understudies to plan and make the last metal layer cover of a semicustom computerized or simple CMOS configuration utilizing wafers that have proactively been preprocessed up to veil 6 (Contact Cut) by the recently enlisted understudies. This will give the understudies' CMOS circuit plans additional opportunity to be tried. Because of the wafers' preprocessing, just a single cover layer should have been made and fabricated in the lab, saving time. Less advances must be taken prior to testing could begin, hence testing should be possible in additional time. Since the semi-specially craft stream was speedier than the earlier complete hand craft stream we were using, how much time saved was additionally expanded. Beforehand, an entire customized plan must be done in one more course the semester before to be utilized on an ongoing wafer run. One more method for stretching out the testing window was to request that understudies get done with testing-accommodating plans like pseudo-arbitrary piece stream generators.

The understudies who were presently selected preprocessed the wafers for use by the understudies of the following year to guarantee that there would be wafers accessible for them to utilize. The fabrication processes were fanned out across the whole semester on the grounds that the wafers were for the next year and would have no need to be tried. Earlier semesters, the technique must be done in 12 weeks to consider fourteen days of testing. The TAs and our professional had the option to complete the assembling processes for the wafers for the next year when it was unrealistic for these understudies to do as such during the semester. At the point when hardware failed during lab gatherings, the teacher had freedom to choose how to manage the class accordingly.

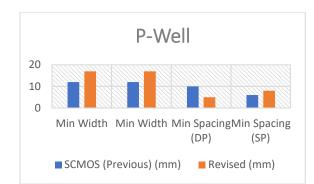

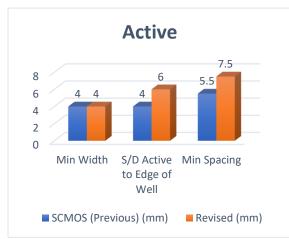

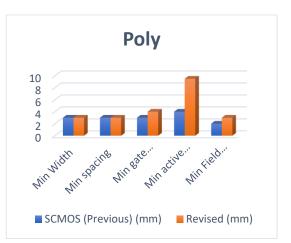

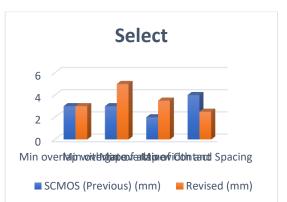

We boosted our circuit yield by altering the layout rules of our process based on the statistics of our alignment registration errors because poor circuit yield increased testing time. Using SCMOS (Scaleable-CMOS) principles, other academic labs have also reported low yields (50%)[4]. Making sure that each device or link has at least two contacts is another enhancement. In order to make it easier to construct and reduce contact resistance, we also increased the contact size from 1.6 mm to 2 mm.

We needed to plan evaluation techniques to ensure all understudies were taking part in lab in light of the fact that a huge piece of every understudy's grade in this subject depends on a gathering grade. We began by having understudies answer namelessly to a short survey about how they thought other colleagues were contributing. Every understudy recognized that their colleagues were effectively involved. This was as opposed to what we had found in the lab, so we made a lab useful test with four undertakings to essentially decide if the understudies had the principal capacities that they would have advanced by completely captivating in the lab exercises. The four errands were to quantify an oxide thickness, find enlistment mistakes in covers, separate sheet opposition from test structures utilizing a HP4145 analyzer, and execute a direct Athena process deck.

The skills that will be examined were made known to the students two weeks in advance. Additionally, students were informed that they might bring any supporting paperwork to help them demonstrate the duties. Students received either a "Go" or a "No-Go" grade. A team was formed out of all the pupils who obtained two or more "No-Go" scores. From that point on, it was crystal clear who was actually working in the facility. The "No-Go" team first appeared to come together and engage in class more than they had earlier in the semester, but after a few weeks they gave up. The design projects for the "No-Go" team were not finished. Unfortunately, it was too late to affect students' conduct; this only measured student engagement. The following semester, we validated students' skills before they began their projects since we thought it would be preferable to enhance student participation rather than only measure it.

Various techniques were utilized to increment understudy impact. The first was to change the essentials from having a required "Prologue to IC assembling" course to having three distinct ways into the course to build the quantity of understudies who enlist straightforwardly into the course. The three choices are past IC fabrication/processing experience, IC circuit configuration (should be know all about Rhythm apparatuses), or high level gadget physical science aptitude joined with Tcomputer aided design (Silvaco/Athena) mastery. Since executing the new prerequisite design, our enlistment has expanded from 5 to 21 understudies.

# 4. **RESULT & DISCUSSION**

As of now, only one understudy design from an expected EE research center course has been made, however on the off chance that the semi-custom IC educational program was taken on by a fundamental EE lab course, this could expand to remember all BSEE understudies for our specialty. We are currently making a typical cell library for our Gate Array using Cadence Design Systems Place and Route Tool to help this. The impact on understudies, as we would like to think, may be compelled by the accessibility of IC test gear and other teachers' eagerness to allow their understudies to utilize our design approach.

Incorporate exceptional gadget structures for future joining with the Gate Array or Simple Leaf Cell at whatever point another veil set was required was one more method for expanding understudy impact. LDMOS designs and Charge Coupled Devices were among them.

| Layer  | Rule                   | SCMOS<br>(Previous)<br>(mm) | Revised<br>(mm) |

|--------|------------------------|-----------------------------|-----------------|

| P-Well | Min Width              | 12                          | 17              |

|        | Min Width              | 12                          | 17              |

|        | Min<br>Spacing<br>(DP) | 10                          | 5               |

|        | Min<br>Spacing<br>(SP) | 6                           | 8               |

#### A. Previous and Revised Layout Rules

| Layer  | Rule                                | SCMOS<br>(Previous)<br>(mm) | Revised<br>(mm) |

|--------|-------------------------------------|-----------------------------|-----------------|

| ACTIVE | Min<br>Width                        | 4                           | 4               |

|        | S/D<br>Active to<br>Edge of<br>Well | 4                           | 6               |

|        | Min<br>Spacing                      | 5.5                         | 7.5             |

| Layer  | Rule                | SCMOS<br>(Previous) (mm) | Revised<br>(mm) |

|--------|---------------------|--------------------------|-----------------|

| P-Well | Min Width           | 12                       | 17              |

|        | Min Width           | 12                       | 17              |

|        | Min Spacing<br>(DP) | 10                       | 5               |

|        | Min Spacing<br>(SP) | 6                        | 8               |

| Layer | Rule                  | SCMOS<br>(Previous)<br>(mm) | Revised<br>(mm) |

|-------|-----------------------|-----------------------------|-----------------|

| POLY  | Min Width             | 3                           | 3               |

|       | Min spacing           | 3                           | 3               |

|       | Min gate<br>extension | 3                           | 4               |

| Min active extension to Poly | 4 | 9.5 |

|------------------------------|---|-----|

| Min Field poly to active     | 2 | 3   |

| Layer  | Rule                      | SCMOS<br>(Previous)<br>(mm) | Revised<br>(mm) |

|--------|---------------------------|-----------------------------|-----------------|

| SELECT | Min overlap<br>with gate  | 3                           | 3               |

|        | Min overlap of active     | 3                           | 5               |

|        | Min overlap<br>of Contact | 2                           | 3.5             |

|        | Min width<br>and Spacing  | 4                           | 2.5             |

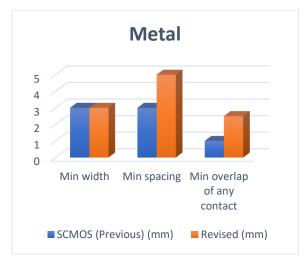

| Layer | Rule                          | SCMOS<br>(Previous)<br>(mm) | Revised<br>(mm) |

|-------|-------------------------------|-----------------------------|-----------------|

| METAL | Min width                     | 3                           | 3               |

|       | Min spacing                   | 3                           | 5               |

|       | Min overlap of<br>any contact | 1                           | 2.5             |

## CONCLUSION

By allowing understudies to design, construct, and test semi-specially craft flows, (for example, those for a gate array or a simple leaf cell) as well as direct two veil MOS process design flows, we had the option to further develop understudy learning. The ideal opportunity for testing was stretched out by changing to a semi-custom flow and a less confounded semiconductor fabricating flow. We accept that having three distinct doors to our senior level IC processing research facility permitted us to help the impact of our understudies extensively. Offering a Gate Array or Simple Leaf cell design insight to understudies in center EE courses, as we would see it, ought to be feasible to fundamentally support the understudy impact of this course (for example an ongoing mirror in our Circuits I. course). The effect of fostering a design process unit that different schools can use could be expanded. These changes, as we would like to think, have empowered understudies to get more information in our CMOS processing course. Also, we have expanded the course's impact past its ongoing understudy body. Moreover, on the grounds that they had more than adequate opportunity to apply the two flows in full all through one semester, understudies had the option to interface the thoughts of a CMOS circuit design flow and a semiconductor process design flow.

#### **FUTURE WORK**

This project's future work will include establishing relationships with secondary school instructors and students. Two forums will be created to facilitate this. After the Microelectronic fabrication course has been established and its operation shown, these forums will be developed. The first forum is a two-

course for continuing education that week microfabrication introduces teachers to the laboratory. Here. science and mathematics instructors, as well as future science and mathematics teachers, will be exposed to the techniques employed in the fabrication of transistors and integrated circuits. The attendees of the workshop will be provided with a learning aid kit. Figure 4. Teflon Bucket Figure 3. Student employing furnace microelectronic manufacturing techniques. The package would include materials to assist the instructor in presenting the foundations of microfabrication to middle and high school students. Presentation materials such as PowerPoint presentations and interactive websites that convey the essence of the technology will be included in the teaching materials. This session will emphasise comprehension of the problem-solving process and the fact that engineering is a type of applied problem-solving. By visiting the facility, secondary school educators will gain a better knowledge of the methods required to create the fundamental circuits employed in contemporary technology. This would be imparted to students at a young age and inspire them to pursue careers in science and engineering. This programme will utilise the facility during the summer months, when typically fewer engineering students enrol in courses and when teachers seek additional training.

🔚 ActaEnergetica

#### REFERENCES

- DZIEDZIC, A. Grubowarstwowe rezystywne mikrokompozyty polimerowo-węglowe. Oficyna Wydawnicza Politechniki Wrocławskiej, Wrocław 2001, 152 p. (in Polish).

- ROOS-KOZEL, B. L, CASAVECCHIA, F. M. Parameters affecting silver flake and powder performance in silver filled polymer. Solid St. Technol., 1984, vol. 27, no. 8, p.167-171.

- DZIEDZIC, A., GASPEROWICZ, A., ZNAMIROWSKI, Z. Polimerowe grubowarstwowe kompozycje przewodzące na podłożu elastycznym. In Mat. III Konf. Technologia Elektronowa ELTE'87. Poznań (Poland), 1987, p.407-409 (in Polish).

- DE FOSSE, S. F., WILLIAMS, G. T., GOSTOMSKI, D. A., COBB, R. H. Development of a membrane switch-type full-travel keyboard. IBM J. Res. and Develop., 1985, vol. 29, p. 478-487.

- ZNAMIROWSKI, Z., DZIEDZIC, A., POPOWICZ, W. Zespół membranowego przełącznika komputerowego. In Mat. III Konf.

Techn. Elektronowa ELTE'87. Poznań (Poland), 1987, p. 101-103 (in Polish).

- FINKENZELLER, K. RFID Handbook: Fundamentals and Applications in Contactless Smart Cards and Identification. 2nd ed. New York: John Wiley & Sons, Inc., 2003.

- PARET, D. RFID and Contactless Smart Card Applications. John Wiley & Sons, Ltd, 2005.

- HUNT, V. D., PUGLIA, A., PUGLIA, M. RFID -A Guide to Radio Frequency Identification. New York: John Wiley & Sons, Inc., 2007.

- DOBKIN, D. M. The RF in RFID: Passive UHF RFID in Practice. Elsevier Inc., 2008.

- DZIEDZIC, A., NIJS, J., SZLUFCIK, J. Thick-film fine-line fabrication techniques – application to front metallisation of solar cells. Hybrid Circuits, 1993, no. 30, p. 18-22.

- PUDAS, M., HALONEN, N., GRANAT, P., VÄHÄKANGAS, J. Gravure printing of conductive particulate polymer inks on flexible substrates. Progress in Organic Coatings, 2005, vol. 54, p. 310- 316.

- REDINGER, D., MOLESA, S., YIN, S., FARSCHI, R., SUBRAMANIAN, V. An ink-jetdeposited passive component process for RFID. IEEE Trans. on Electron Devices, 2004, vol. 51, p. 1978-83.

- MÄNTYSALO, M., MANSIKKAMÄKI, P. An ink-jet deposited antenna for 2.4 GHz applications. Int. J. Electron. Commun., 2009, vol. 63, p. 31-35.

- ROGERS, J. A. Stamping techniques for micro and nanofabrication: methods and applications. In Springer Handbook of Nanotechnology. Springer, 2004.

- 15. http://screenweb.com/index.php/channel/4/id/689, 04.2009