# Recent Advancement in the Field of Analogue Layout Synthesis

# **Mariusz Filipowicz**

DSc(Eng), Associate Professor, The AGH University of Science and Technology, Kraków, Poland

## Waleed F. Faris

Professor, International Islamic University Malaysia, Kuala Lumpur- 53100, Malaysia

# Keywords

Analogue Layout Synthesis, Hierarchical analogue

# Abstract

To diminish layout configuration time, simple layout creators favor alluding to inheritance plans and layouts instead of beginning without any preparation, or completely applying arrangement and directing apparatuses on the grounds that heritage layouts contain essentially plan skill. Subsequently, this paper presents the principal information based layout synthesis technique to produce new layouts by coordinating existent plan aptitude contained in the quality-supported heritage layouts however much as could reasonably be expected. Exploratory outcomes show that the proposed system with information mining can accomplish high layout reusage rate and thus the planners' layout inclination can be effectively held. Hierarchicalanalog layout generators go on from leaf cells ("locals") to sensibly greater blocks that are set and directed. The idea of unrefined cell layout is fundamental for plan execution. The framework recommended in this paper upgrades and arranges locals' presentation estimations during leaf cell layout. Consolidating layout parasitics and layout-subordinate impacts, it furnishes the spot and course engine with an assortment of better layout determinations as well as wire estimating rules for affiliations beyond the telephone. Our technique outflanks the opposition for FinFET-based plans of a high-repeat intensifier, a StrongARM comparator, and a completely differential VCO and is compelling with time-escalated manual layout.

Received by the editor: 16.03.2022 Received in revised form: 03.06.2022 Accepted: 20.06.2022

#### 1. INTRODUCTION

Simple planners prioritise schematic and layout plans until a variety of objective details are satisfied. Instinct and experience should be used by individuals who create schematics to make assumptions about parasites, and those who plan layouts should use those assumptions to portray the schematic while taking into account sacrifices made during schematic design. The iterative cycle is hampered by the manual layout's slow loop back (days/long stretches) by allowing only a few emphases. By creating great layouts in minutes, simple layout mechanization might possibly empower more plan cycles to completely investigate the plan space.

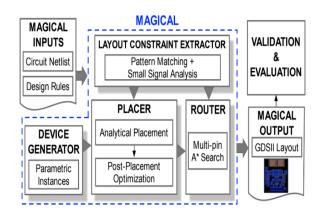

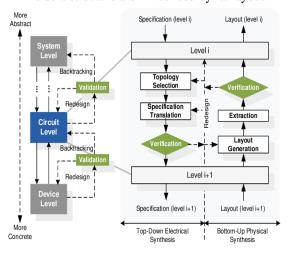

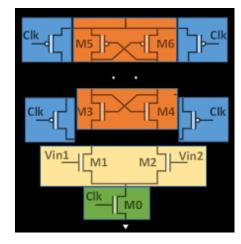

Simple layout robotization devices frequently function in hierarchical structures. One such hierarchical stream is shown in Fig. 1 and begins to gather building blocks with the lowest level designs, the natives. Natives are the fundamental components of a simple circuit, consisting of groups of actives or passives (such as differential matches and current mirrors). The circuit netlist is at first examined in the stream, either actually or thoughtfully, to show the circuit's dynamic framework from locals to additional critical level blocks, the accessibility between building blocks, and layout necessities. A cell generator then creates crude layouts with the expected gadget sizes, adjusting necessities, typical centroid, or interdigitation needs utilizing a parameterizable crude library. FinFET hubs commonly employ meshlike guidance to minimise resistive parasitics in lower metal layers. Larger blocks of natives are formed, and these blocks are organised hierarchically and globally according to mathematical and operational imperatives. The layout is finally finished with specific guidance.

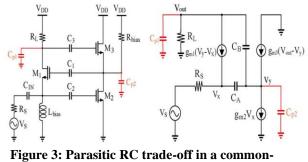

To match schematic assumptions, there is plenty of space for basic circuit execution optimization. The wellsprings of M1 and M2 in Fig. 2 are sometimes improved to confine R for the typical source enhancer. We center around the channel net Vout and research the effect of different wire widths. Execution wanders off from the schematic for restricted (high R, low C) and wide (high C, low R) courses, however a streamlined width approaches This research takes into schematic execution. account advancements at the basic cell level. We adhere to the creator's intent by concentrating on the schematic implementation (predisposition conditions, execution compromises). In Fig. 1, we integrate two fresh improvement projects into the layout age stream: • Crude level layout simplification selects several high-performance crude design for the spot/course motor, offering a variety of options with different viewpoint proportions for boosting the overall layout. We depict the display of the gadgets by combining layout subordinate influences (LDEs) and upgrading wire widths inside the crude. • Simplifying crude ports enhances a crude in a globally directed design and enlarges wires for connections between ports and external blocks. For the precise switch, the widths must be reduced. There is a rumour that previous work has not addressed this exact issue definition. Similar work identifies a circuit's parasitic R and C limitations using high level schematic reenactments, but this approach is computationally expensive and unsuitable for a hierarchical layout stream. By using post-layout reproductions and keeping parasites and LDEs in mind at the same time, we improve crude layouts and the courses that go along with them in light of crude execution. We show our technique utilizing a FinFET development on the grounds that a clear plan is rapidly moving to these center points, where layout setup is more troublesome. As controlling and gadget parasitics reduce, LDEs become more noticeable, which could bring about huge execution changes

from schematic to layout. We stick to the gridded FinFET layout design restrictions; for instance, we utilize equivalent quantities of wires and vias to create authentic additions in wire width.

# 2. ANALOG LAYOUT DESIGN AND CHALLENGES

- 1. Analog IC layout design is still heavily manual

- 2. Compared with digital

- 3. Time-consuming and error-prone

- 4. Complex design rules

- 5. Difficulties for automated analog layout

- 6. Sensitive layout effects

- 7. Complex performance trade-offs

- 8. No governing optimization targets

- 9. As a result analog layout rely on

- **10**. Human experience

- **11**. Heuristic constraints

- 12. Aesthetic engineering

#### **Figure 1: Fully Automated Layout Generation**

# 3. PERFORMANCE METRICS FOR PRIMITIVES

- A. Primitives Natives serve as the basic building blocks for more complex simple plans like OTAs, comparators, and LNAs. 20–30 rough netlists and procedural layout age code for various definitions are included in a primitive library (e.g., different gadget sizes, exhibit structures, balances). Natives can be divided into a few useful classes:

- Differential pairs (DPs), including switched forms in data converters and cascoded versions in amplifiers/comparators.

- Current mirrors (CMs), including cascoded/lowvoltage cascode structures and active and passive CMs.

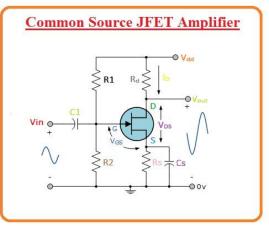

- Common source, common gate, and common drain amplifiers.

- Loads include current sources, structures connected by diodes, and cascaded structures connected by diodes.

- Switches, cross-coupled pairs, current-starved inverters, and cross-coupled inverters are examples of analogue structures that resemble digital structures.

- Passives: capacitors, inductors, and resistors. We cultivate a number of rudimentary level execution metrics to the point where, provided we keep their variance from the schematic's value inside bounds, the circuit's operation remains predictable. The limits of the elements inside a structure are influenced by its layout.

Figure 2: A hierarchical analogue layout synthesis flow.

Gadget limits, which are affected by LDEs, manage crucial execution measurements, for example, the practical transconductance, Gm, which relies upon the semiconductor's transconductance, gm, and the parasitic deterrent of wires prompting its source. In Fig. 2, a common source intensifier stage (M1) and a ceaseless source load are two occasions of the normal source enhancer (M2). The commonsource speaker stage's central show measurements are the suitable transconductance (Gm), yield resistance (Rout), and result capacitance (Cout). Different contributors outside the fundamental are possibly at the schematic worth while responsibilities from M1 are improved to be near the schematic worth. The presenting metrics for the ongoing source load are the current, IM2, resistance, Defeat, and result capacitance, Cout.

Some exhibition measurements for the two locals are shown in Table I. The simplified arrangement demonstrates the optimal alignment of the layout and schematic execution. To identify the crude level presentation metric that has an impact on TABLE I: Crude level measurement, we examine each crude's circuit-level use cases.

Simple execution metric evaluation DC predisposed conditions have an impact on crude execution. This information comes from circuit-level schematic recreations. We add the following to the crude library to facilitate the investigation of crude execution measurements:

- The significant presentation measurements for every crude, and a load for every measurement to demonstrate its relative significance.

- Tuning terminals for the crude, posting of the terminals where RC parasitics can be compromised to advance execution, and descriptions of the connections made to the tuning terminals (i.e., the ideal worth of one relies upon that of the other).

- A rudimentary testbed for each presentation metric, i.e., a Flavor document with measure proclamations and excitations intended to calculate the measurement by circuit reenactment. Since natives are small (e.g., with less than four semiconductors), these Zest replicas are speedy while also incorporating effects like LDEs that are not consistently captured by astute models. These additions can be applied to multiple cycle hubs and are neither geography- or innovation-dependent.

- Process variations: Architects consider arbitrary varieties during circuit estimating. They can likewise determine different layout examples to limit deliberate varieties.

source amplifier

We give the Ith metric a weight, high I = 1, medium I = 0.5, or low I = 0.1. A greater number denotes a relative difference that is more significant. When

establishing the library passage, the creator could provide this measurement. A detached CM will have a big ongoing percentage weight (I = 1) and a low resultant capacitance weight (I = 0.1), but a functional CM will have a medium load on yield capacitance (I = 0.5). In Table II, we give the exhibition size, loads, and tuning terminals for a variety of typical sites. Other natives from the same family can use this knowledge. For example, DPs and their cascodes will have access to comparative library passages. The DP circuits of comparators and low-power speakers will emphasise the Gm and information offsets heavily. In Fig. 4, we display a model setup for calculating the Gm of the DP. To test the air conditioner channel current, we put an air conditioner voltage at the door.

#### 4. METHODOLOGY

In Fig. 1, we present the two periods of our system: (1) harsh level layout progress, which ensures that the best-performing unpleasant layouts are chosen, changed, and shipped off the placer. (2) crude port improvement, which utilizes the hid overall course data to measure the wires associated with the ports and give information to the switch. The structure improves abnormal plans with the goal that their show assessments like those in the schematic. For example, in Table II, the three most significant execution gauges for a DP are Gm, Cout, and input offset. with expanding layout, (A) (B) (c) Fig. 5: DP calculated in (a). (a) The depiction of M, NF, and NFIN. (c) Choices for a DP semiconductor plan with 96 FinFETs. Parasites, Gm drops, Cout increments, and data offset diminishes all debase circuit execution. To fabricate a cost limit that is weighted by the significance of the estimation as recently depicted, we assess the post-layout potential gains of these measurements. Cost = X k i=1 I xi (5) where I is the weighted normal of every one of the k show measurements and xi is the presentation metric abnormality When xi = |xi,sch|, |xi,layout|, xi,sch if xi,sch 6= 0 greatest h 0, |xi,spec|, |xi,layout|, xi,spec If xi, sch = 0, I (6) For this situation, the benefits of the estimation in the schematic, layout, and specific, freely, are signified by the contractions xi,sch, xi,layout, and xi,spec.

When xi,sch = 0, the succeeding situation, which is covered by the critical case (covering the departure from the schematic), applies. For instance, for DP input offset, where we describe xi,spec as 10% of the irregular offset. A. Further developing the ungainly plan one or two layouts can be made in a FinFET improvement by changing the layout boundaries, as displayed in Fig. 5(b): nfin, the quantity of bleeding edges per finger; nf, the quantity of fingers; and m, the collection, or dull designs, for the DP displayed in Fig. 5(a) with indicated (W/L). Fig. 5 shows three DP semiconductor frameworks with 96 FinFETs every (c). Rough assurance picks the layout parasitics and LDEs with the best exhibition, and unrefined tuning works on coordinating parasitics by changing the reasonable wire widths (i.e., the amount of equivalent wires). Recognizing the rough: A characterized essential unrefined cell generator, for instance, can create an assortment of layout plans in the style of Fig. 5(c) for a foreordained W/L extent for every unrefined in the library. Due to layout restrictions like arrangement design (such as normal centroid or interdigitated) and perspective proportion, there are various layout alternatives for each component (by changing nfin, nf, and m). Each of these options has a different tradeoff point for viewpoint proportion and execution shifts brought on by wire parasitics and device LDEs. For instance, diffusion dividing among semiconductors reduces the region and connecting lengths while also lowering the result capacitance, which is generally appealing. However, for effective matching without sharing dispersion in a 1:8 CM, it might be more important to make m = 8 replicas of the reference.

**Figure 4: Structure Using SPICE**

We imitate these plans utilizing Zing and the simple testbench for metric xi for an essential showcase metric (Section II-B). The 96 FinFETs in Fig. 5(c) are displayed in Flavor as a solitary gadget with model limits for nfin, nf, and m. The lifts the xi,sch-to-xi,layout float in (6) and empowers the estimation of xi because of: • Wire parasitics: We eliminate all parasitics, including scattering parting among

semiconductors, the game plan, inside crude coordinating, and outside loads from the schematic, for every layout mixed by the unrefined cell generator. • LDEs: LDEs, like the length of scattering (LOD) cross and well area influences (WPE), cause changes in edge voltage and are clear in FinFET center points. LDEs are introduced in layout extraction, and Zing can be utilized to assess what they mean for execution. In light of the perspective rate displayed in, LDEs in general influence the continuous extent in contemporary mirrors. The utilization of fakers brings about various tradeoffs that lessen LOD influences however increment locale and wire parasitics.

Figure 5: CLK, M and Vin Series Structure

## 5. RESULTS

We apply our method to a variety of straightforward circuits, including those that call for the streamlining of layout parasitics and LDEs. We demonstrate our methods using a StrongARM comparator, a ringoscillator-based VCO, and a high recurrence five semiconductor OTA. We use the open-source Adjust stream system to implement our strategy for a straightforward layout. In each of the examples, the mathematical constraint of matching two nets was physically accomplished, and the power steering was also physically accomplished.

Figure 6: DNA RNA Classification

Single Input

**Three Inputs**

These methods are outside the scope of our technique, but they ensure that the evaluated outcomes cover the entire circuit layout and include corruptions brought on by IR drop on supply lines. We compare the layouts created using our concept to human layout, schematic reconstruction, and the conventional robotized layout approach. The typical approach, which plays out no upgrades for parasitics, is a nonhierarchical layout where semiconductors are dispersed on a mission to fulfil mathematical limits in location and steering.

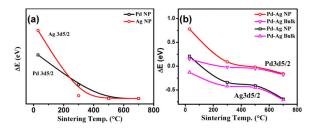

**Figure 7: Sintering Temp Graph**

In Table VIII, the circuits' runtime is presented. It includes the length of time required for improving crude port efficiency, scenario, and cell age and layout. 5T OTA for applications with high recurrence: A comparison of the outcomes of our methodology to the schematic, manual layout, and customary arrangement with mathematical constraints is shown in Table VI. The presentation of the layouts produced by our technique has clearly improved; in this case, the display resembles hand arrangement. According to the traditional technique, the channel length adjustment and aloof CM occlusion create continuing decreases. As a result, the vast array of different metrics is also tainted. Additionally, the parasites at the DP net's wellspring contaminate the Gm and cause growth and recurrence of the solidarity gain.

|        | Differential Pair |           |              | Passive Current Mirror |              |       |

|--------|-------------------|-----------|--------------|------------------------|--------------|-------|

| #Wires | Gm                | Gm/Ctotal | Cost         | Current Ratio          | C Total      | Cost  |

| 1      | 2.50%             | 6.20%     | 2.50%        | 2.50%                  | 2.10%        | 2.11% |

| 2      | 3.10%             | 7.10%     | 3.10%        | 3.10%                  | 3.60%        | 3.50% |

| 3      | <u>3.20%</u>      | 6.30%     | <u>3.20%</u> | <u>3.20%</u>           | 2.80%        | 3.20% |

| 4      | 4.10%             | 7.70%     | 4.10%        | 4.10%                  | 3.10%        | 2.10% |

| 5      | 2.11%             | 7.20%     | 2.11%        | 2.11%                  | <u>3.20%</u> | 3.60% |

| 6      | 3.50%             | 6.60%     | 3.50%        | 3.50%                  | 4.10%        | 2.80% |

| 7      | 3.20%             | 6.60%     | 3.20%        | 3.20%                  | 2.11%        | 2.77% |

#### Table 1: High-frequency OTA & StrongARM comparator.

## Table 2: Transfer Structure and Components

| Transfer Structure       | Scourse Cost<br>Comp Str | Source<br>CCS | Tgt Cost<br>Comp Str | Target<br>CCS |

|--------------------------|--------------------------|---------------|----------------------|---------------|

| Dialog Structure         | 10                       | 5             | 50                   | 20            |

| Cost component Structure | 10                       | 5             | 50                   | 20            |

| Cost Components          | 10                       | 5             | 50                   | 20            |

| Assugbnebt Cost          | 10                       | 5             | 50                   | 20            |

| Updated Additive         | 10                       | 5             | 50                   | 20            |

| Transfer Structure       | 10                       | 5             | 50                   | 20            |

| Cost Component View      | 10                       | 5             | 50                   | 20            |

Minimum Output: 1.9% Maximum Output= 6.15%

#### 6. CONCLUSION

For straightforward execution, especially for FinFET hubs, the design of crude leaf cells is crucial. The purposeful method presented in this paper ensures that sloppy presentation corresponds to schematic execution. The technique's viability demonstrates significant advancements over past efforts. This work can quickly be made available to various advancements, including mass hubs.

## 7. FUTURE SCOPE

Future examination will zero in on working on our instrument and resolving the issues brought up in the distribution. Meanwhile, we have made our plan open source and presently need to appropriately divulge it to the more extensive imaginative local area to get more client input. It would be useful to get input from different craftsmen and investigate how they utilize this instrument in their own work processes and Eurorack frameworks. We trust that by making the task open source, different craftsmen will utilize it and alter it to make their own one of a kind arrangements.

## REFERENCES

- G. G. E. Gielen and R. A. Rutenbar, "Computeraided design of analog and mixed-signal integrated circuits," Proc. of the IEEE, vol. 88, no. 12, pp. 1825–1854, 2000.

- M. Eick, et al., "Comprehensive Generation of Hierarchical Placement Rules for Analog Integrated Circuits," IEEE T. Comput. Aid.D., vol. 30, no. 2, pp. 180–193, 2011.

- K. Kunal, et al., "ALIGN: Open-source analog layout automation from the ground up," in Proc. DAC, pp. 77–80, 2019.

- T. Massier, et al., "The Sizing Rules Method for CMOS and Bipolar Analog Integrated Circuit Synthesis," IEEE T. Comput. Aid.D., vol. 27, no. 12, pp. 2209–2222, 2008.

- M. Meissner and L. Hedrich, "FEATS: Framework for Explorative Analog Topology Synthesis," IEEE T. Comput. Aid.D., vol. 34, no. 2, pp. 213–226, 2015.

- K. Kunal, et al., "A general approach for identifying hierarchical symmetry constraints for analog circuit layout," in Proc. ICCAD, 2020.

- M. P. Lin, et al., "Recent research development and new challenges in analog layout synthesis," in Proc. ASP-DAC, pp. 617–622, 2016.

- Y. Li, et al., "A Customized Graph Neural Network Model for Guiding Analog IC Placement," in Proc. ICCAD, 2020.

- M. Liu, et al., "Towards Decrypting the Art of Analog Layout: Placement Quality Prediction via Transfer Learning," in Proc. DATE, pp. 496–501, 2020.

- Tanaka, H., and Yoshimoto, K. ~1993!. "Genetic algorithm applied to the facility layout problem." Dept. of Industrial Engineering and Management, Waseda Univ., Tokyo. Tate, D. M., and Smith, A. E. ~1993!.

- 11. Genetic algorithm optimization applied to variations of the unequal area facilities layout problem." Proc., 2nd Industrial Engineering Res. Conf., 335–339.

- Tate, D. M., and Smith, A. E. ~1995!."A genetic approach to the quadratic assignment problem."Comput.Operat. Res., 22~1!, 73–83. Thabet, W. Y. ~1992!.

- A space-constrained resource-constrained scheduling system for multi-story buildings." PhD dissertation, Civil Engineering Dept., Virginia Polytechnic and State Univ., Blacksburg, Va. Tommelein, I. D., Levitt, R. E., Hayes-Roth, B., and Confrey, T. ~1991

- SightPlan experiments: Alternate strategies for site layout design." J. Comput. Civ. Eng., 5~1!, 42–63. Tommelein, I. D., and Zouein, P. P. ~1993!."Interactive dynamic layout planning." J. Constr. Eng. Manage., 119~2!, 266–287. Yeh, I.-C. ~1995

- MoveSchedule: A planning tool for scheduling space use on construction sites," PhD dissertation, Dept. of Civil and Environmental Engineering, Univ. of Michigan, Ann Arbor., Mich. Zouein, P. P., and Tommelein, I. D. ~1999